# SERVICE MANUAL FOR

<u>8224</u>

BY: Star Meng

Validation Tool Research Department /EDVD Mar.2006 / R01

### **Contents**

| 1. Hardware Engineering Specification             | 4         |

|---------------------------------------------------|-----------|

| 1.1 Introduction                                  |           |

| 1.2 Hardware System                               |           |

| 1.3 Other Functions                               | 38        |

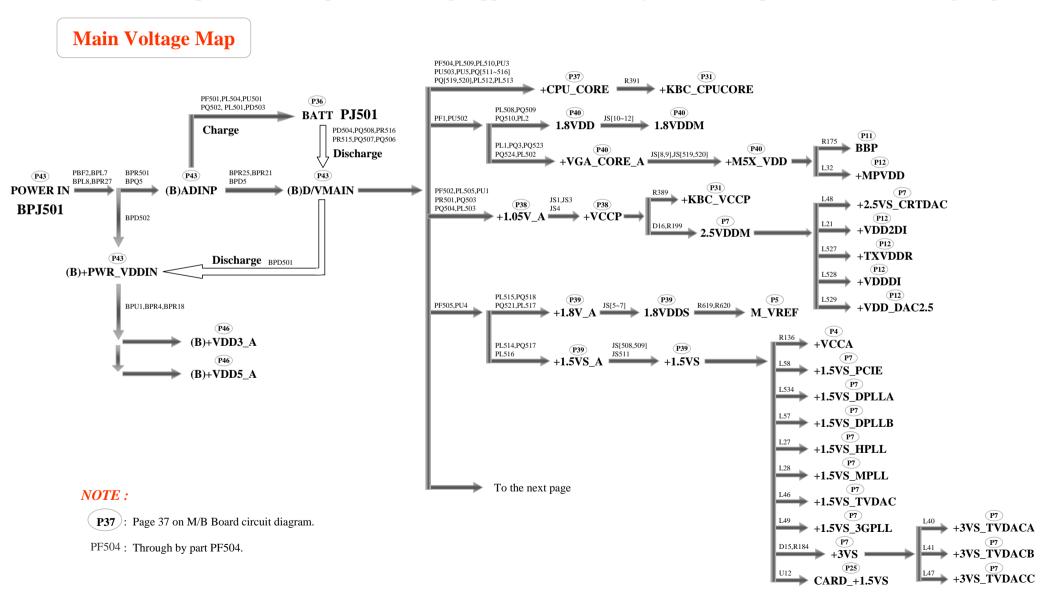

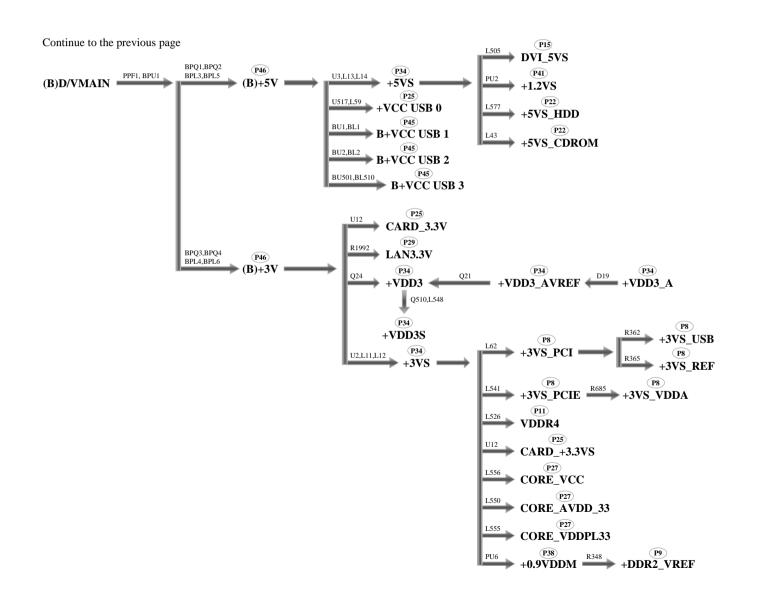

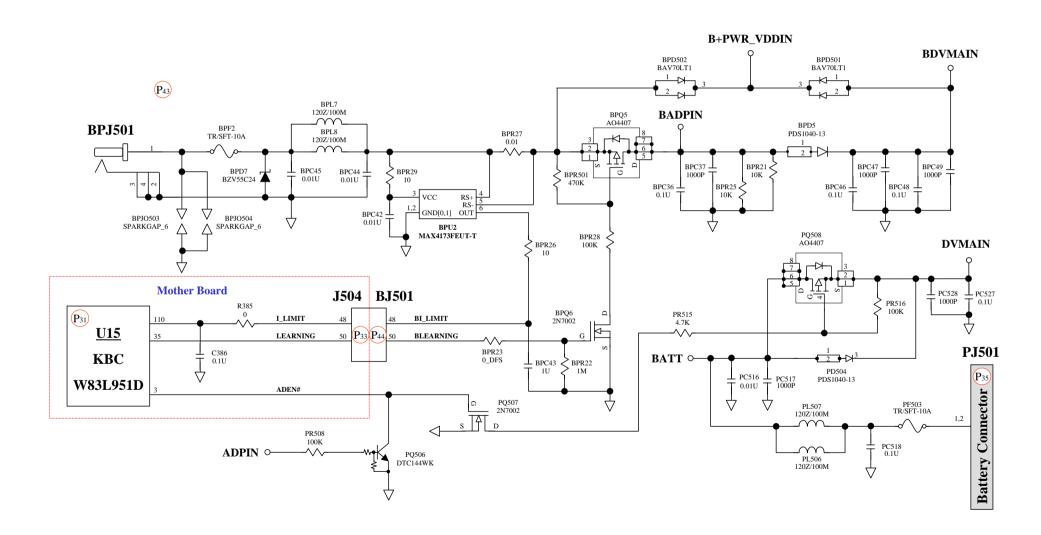

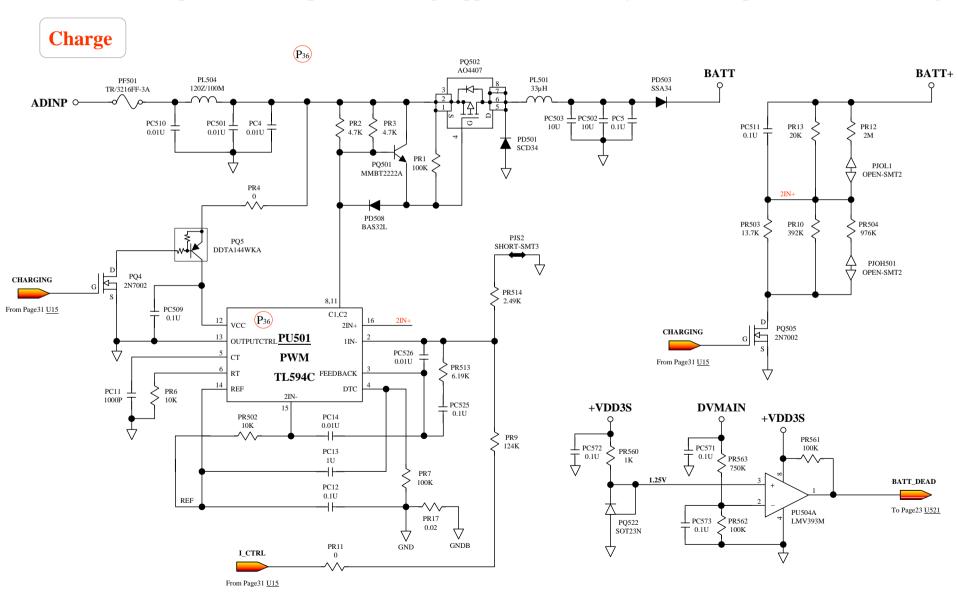

| 1.4 Power Management                              | 44        |

| 1.5 Appendix 1: Intel ICH7-M GPIO Definitions     | 47        |

| 1.6 Appendix 2: W83L951DG GPIO Definitions        | 49        |

| 2. System View and Disassembly                    | 54        |

| 2.1 System View                                   | 54        |

| 2.2 Tools Introduction                            |           |

| 2.3 System Disassembly                            | 58        |

| 3. Definition & Location of Connectors / Switches | <b>78</b> |

| 3.1 Mother Board                                  | 78        |

| 3.2 Daughter Board                                | 81        |

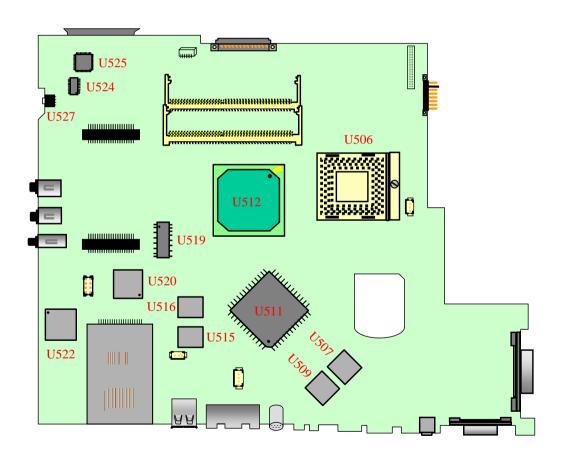

| 4. Definition & Location of Major Components      | 82        |

| 4.1 Mother Board                                  | 82        |

| 5. Pin Description of Major Components            | 84        |

| 5.1 Intel 945/945P North Bridge                   | 84        |

| 5.2 Intel ICH7-M South Bridge                     |           |

### **Contents**

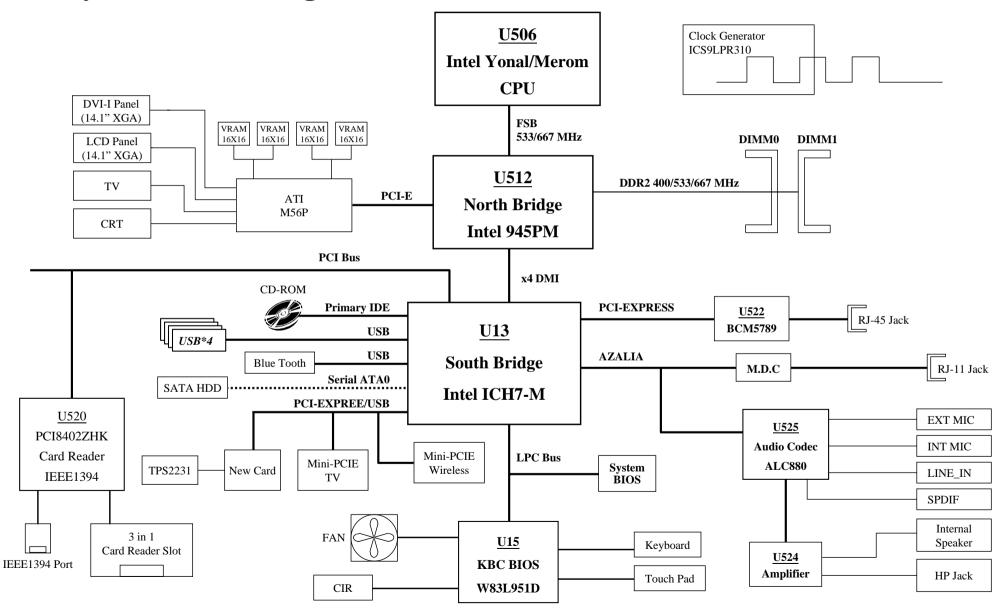

| 6. System Block Diagram                       | 101 |

|-----------------------------------------------|-----|

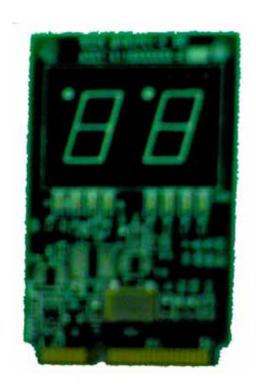

| 7. Maintenance Diagnostics                    | 102 |

| 7.1 Introduction                              | 100 |

| 7.2 Error Codes                               |     |

| 7.3 Debug Tool                                |     |

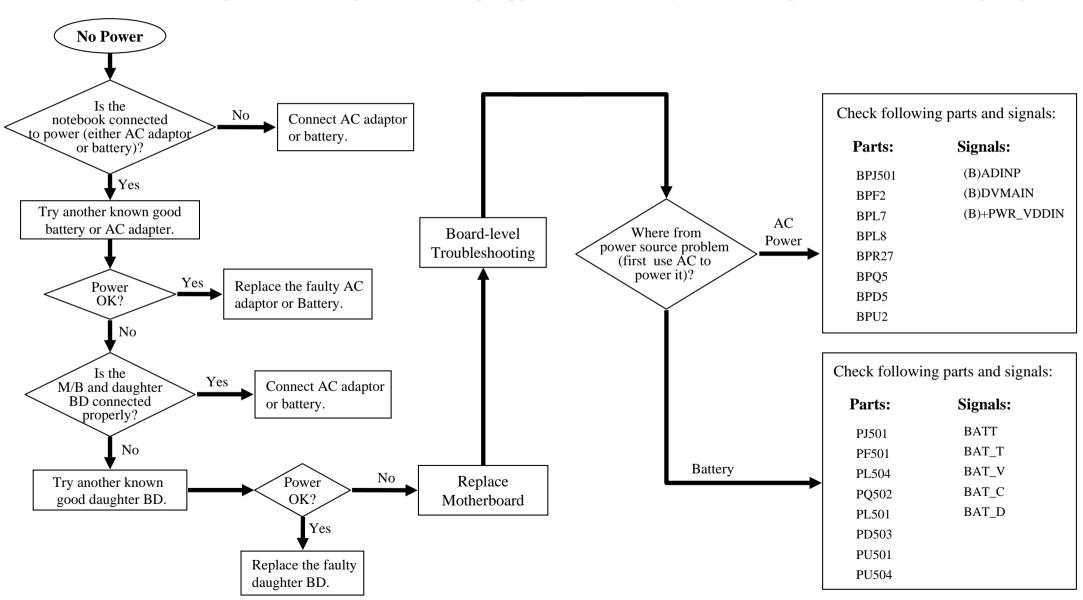

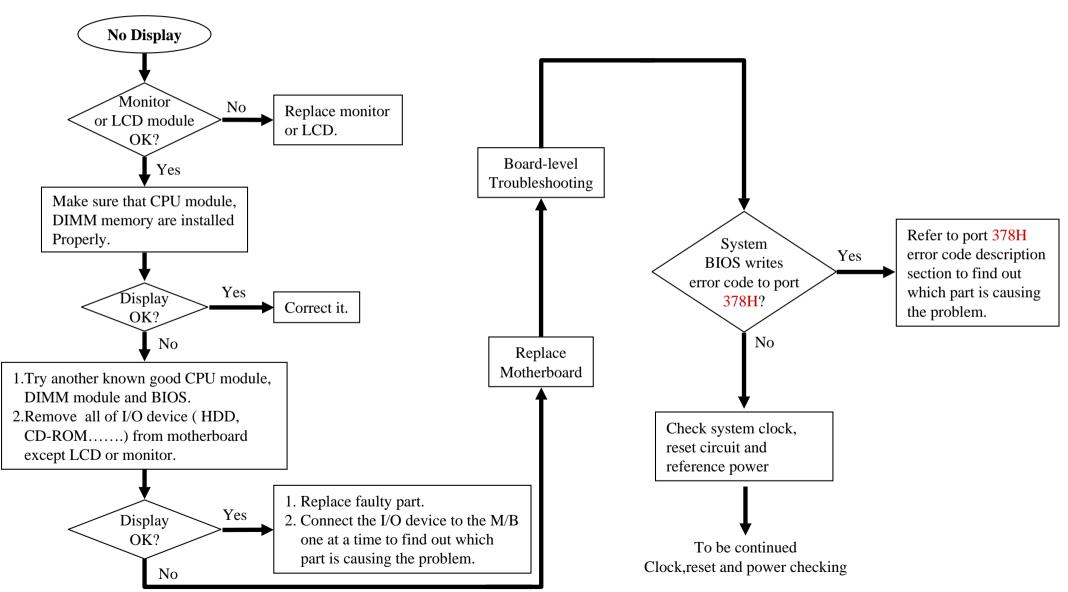

| 8. Trouble Shooting                           | 107 |

| 8.1 No Power                                  | 109 |

| 8.2 No Display                                | 115 |

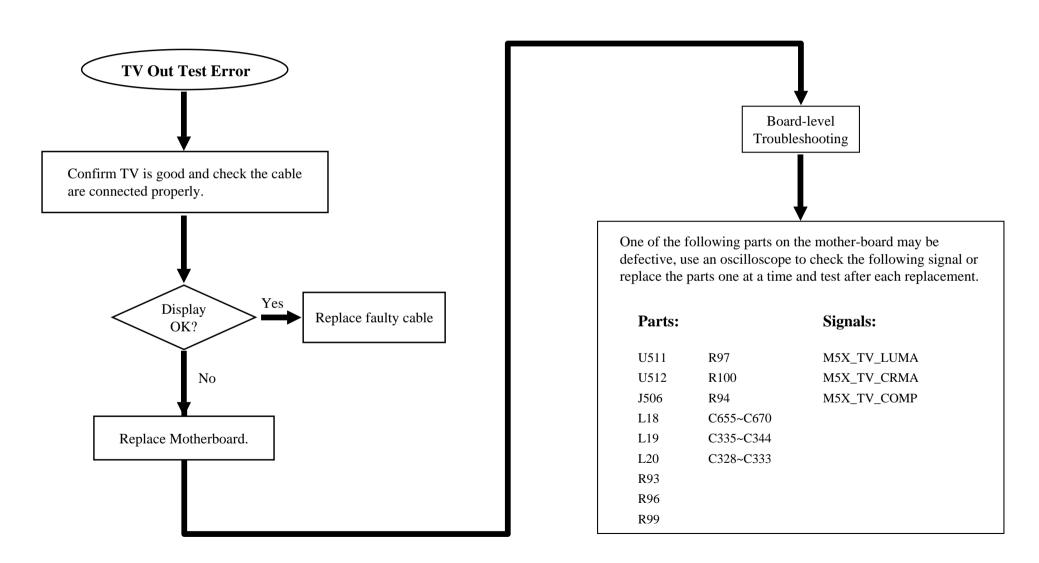

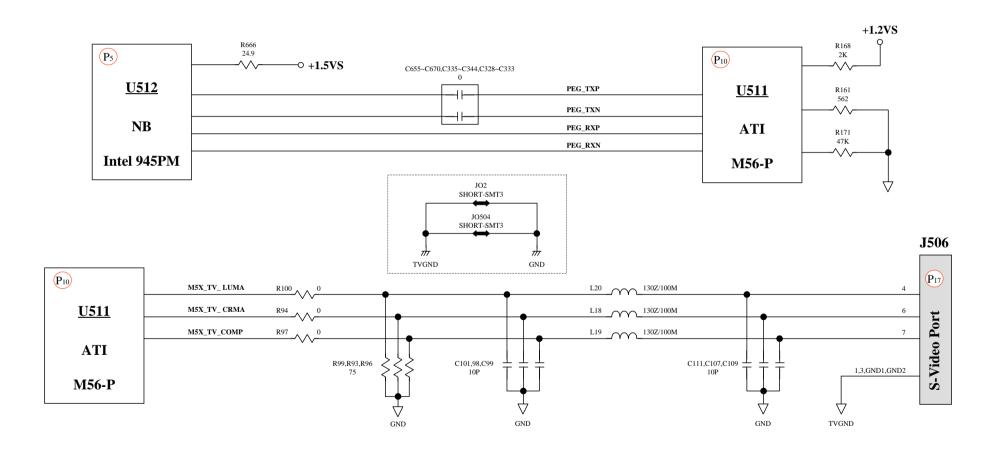

| 8.3 TV Out Test Error                         | 118 |

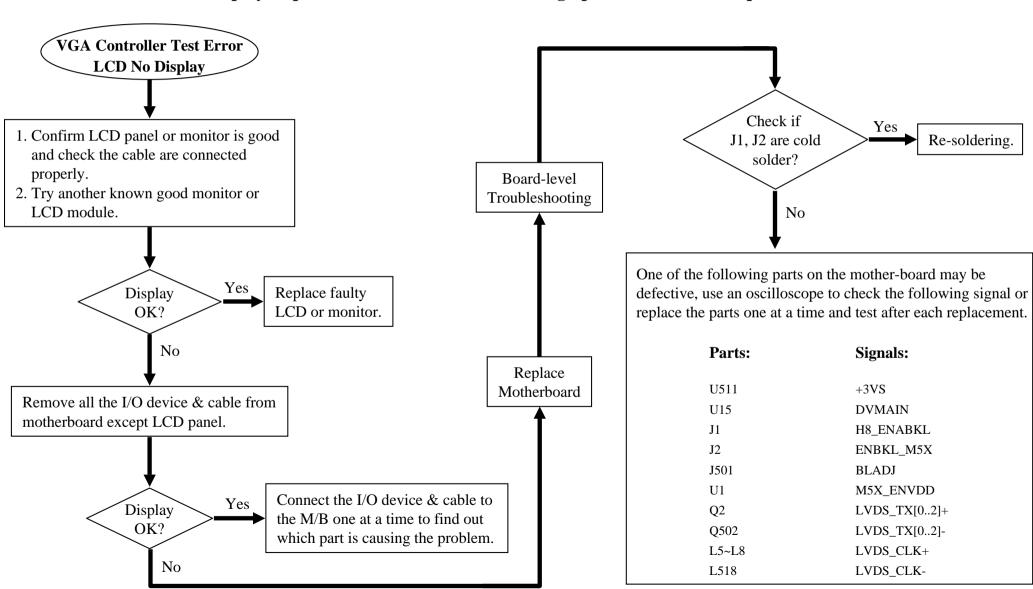

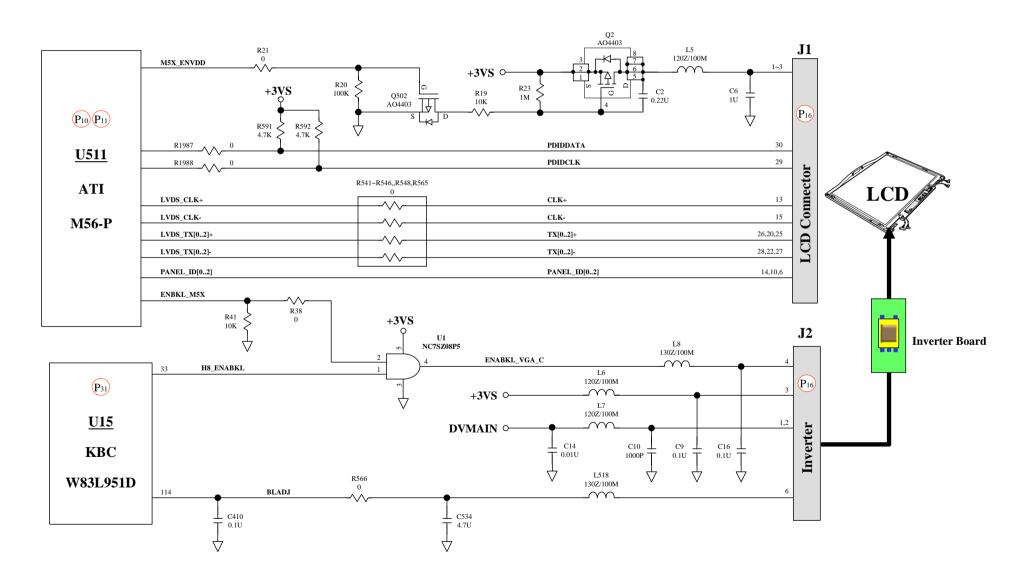

| 8.4 VGA Controller Test Error LCD No Display  |     |

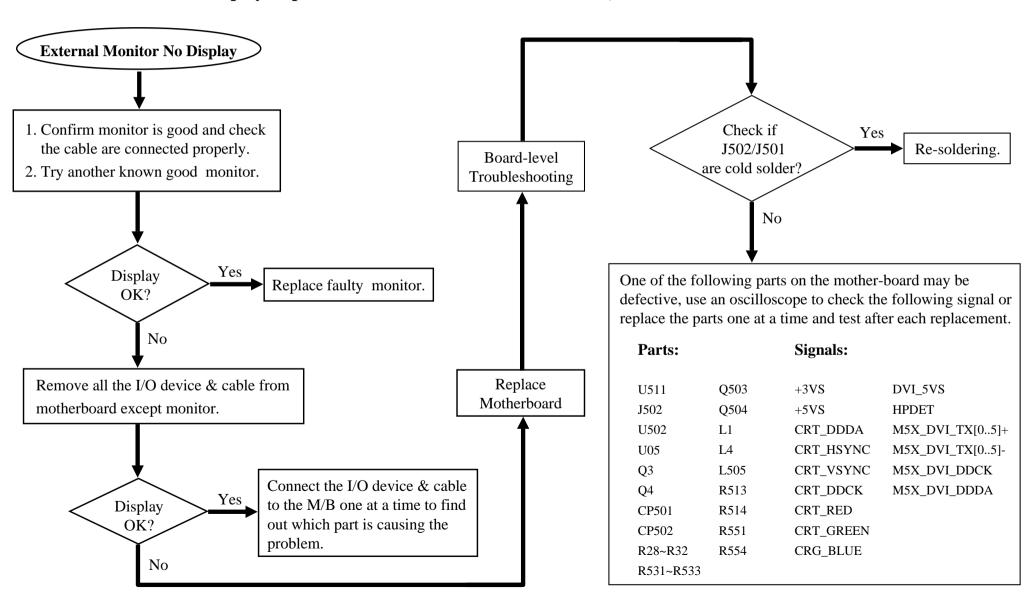

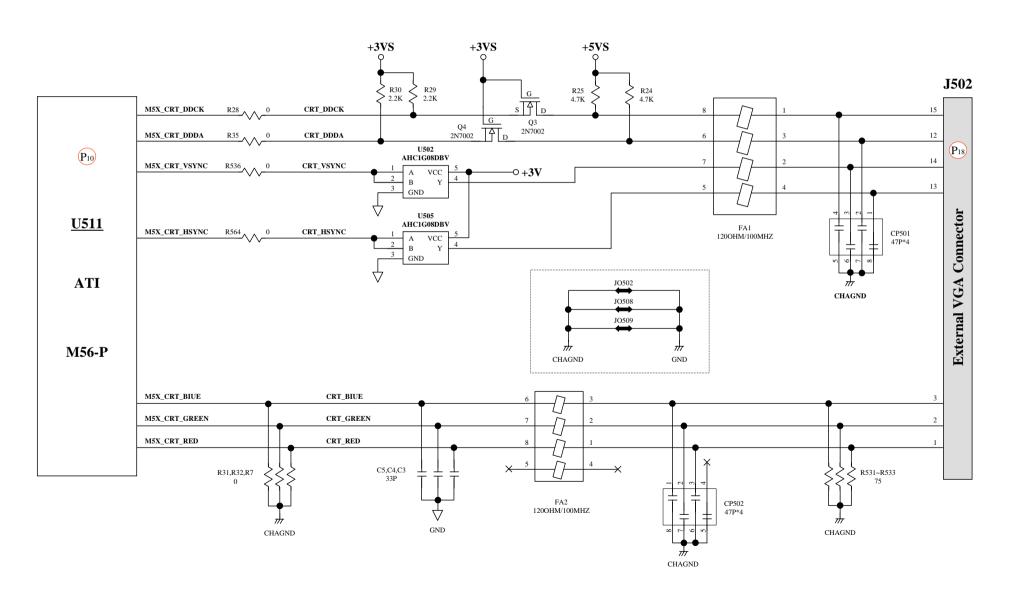

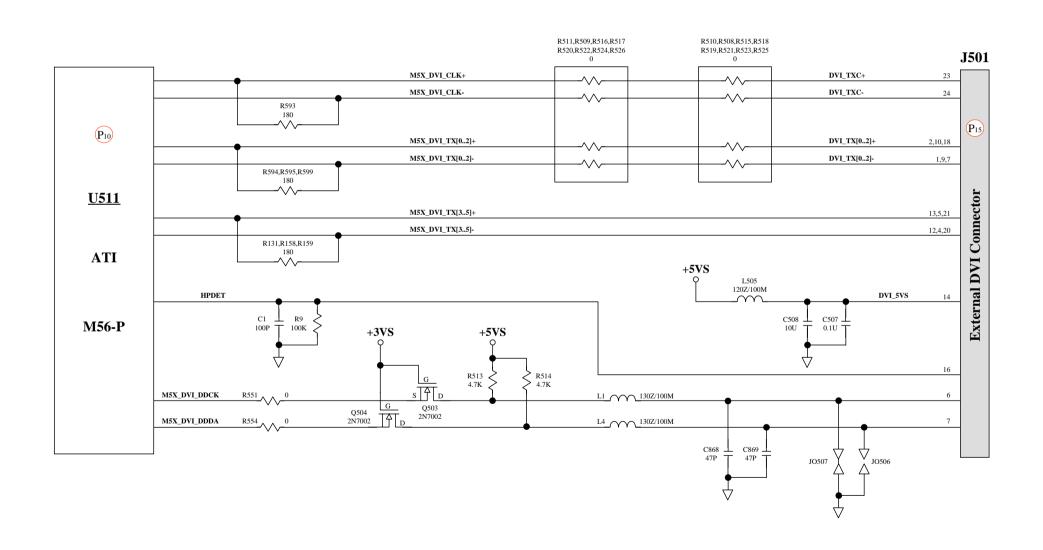

| 8.5 External Monitor No Display               | 122 |

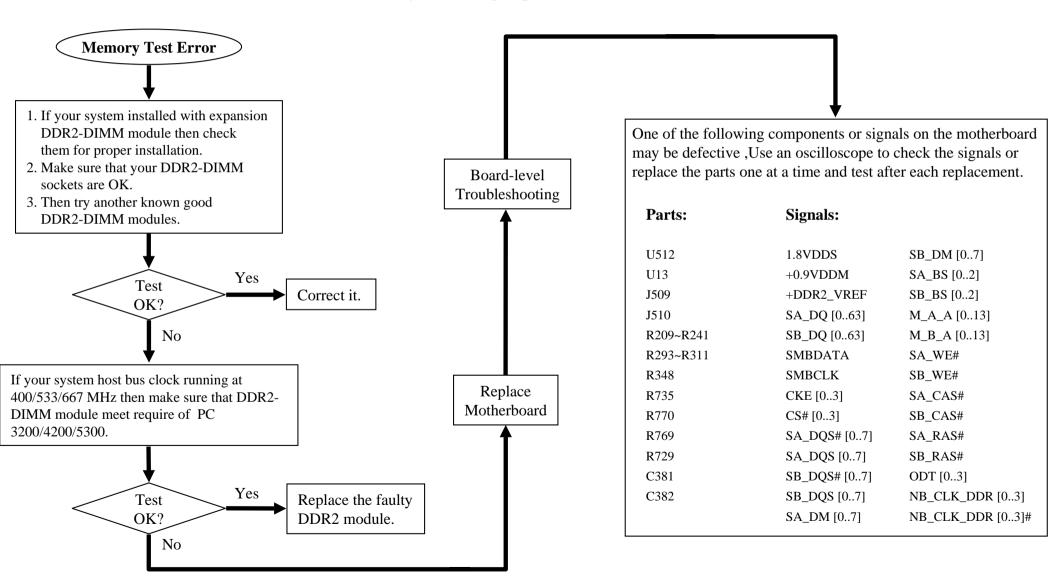

| 8.6 Memory Test Error                         | 125 |

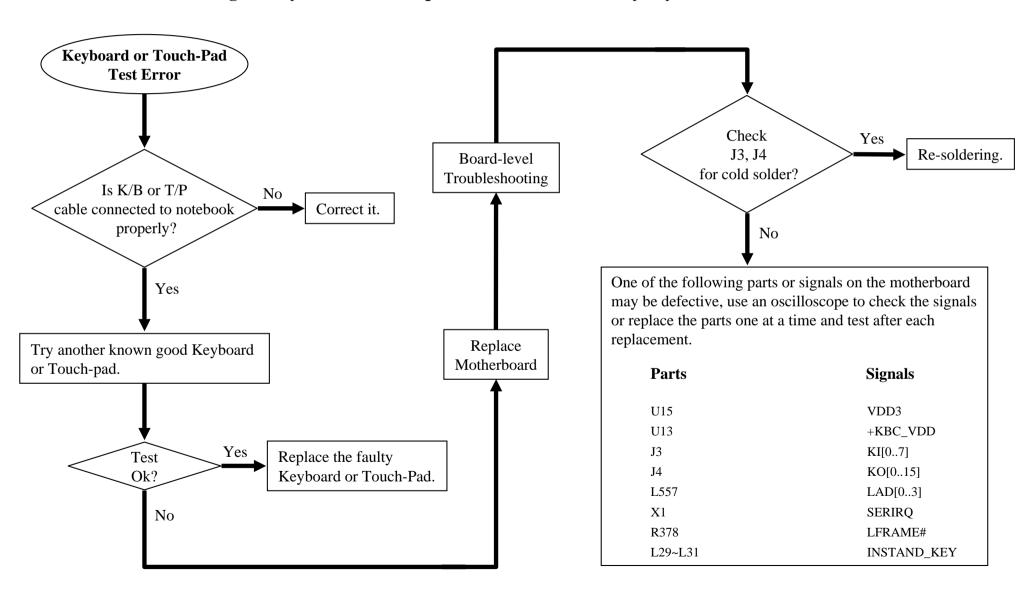

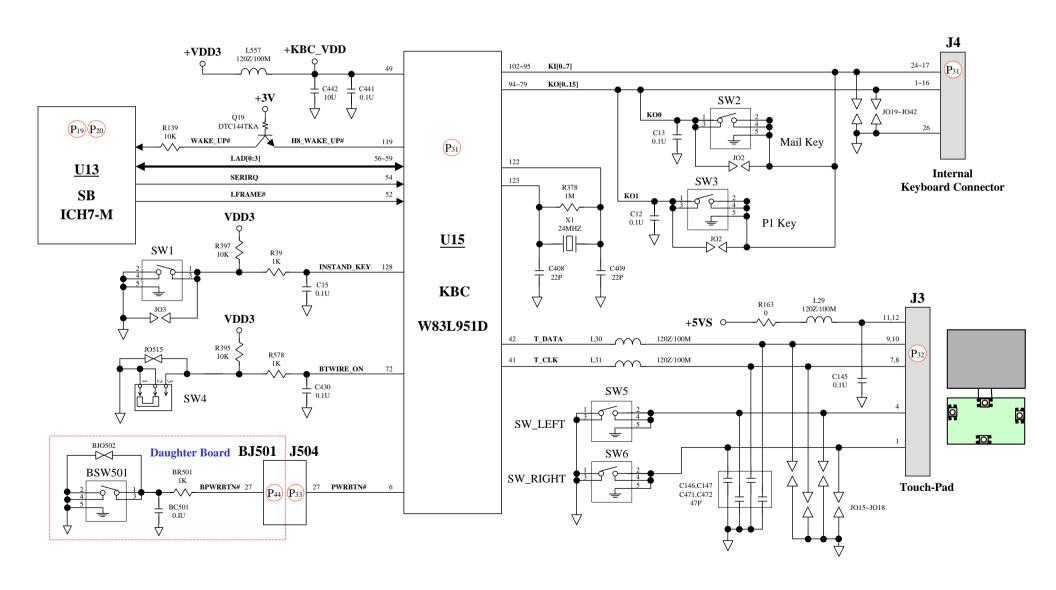

| 8.7 Keyboard (K/B) Touch-Pad (T/P) Test Error |     |

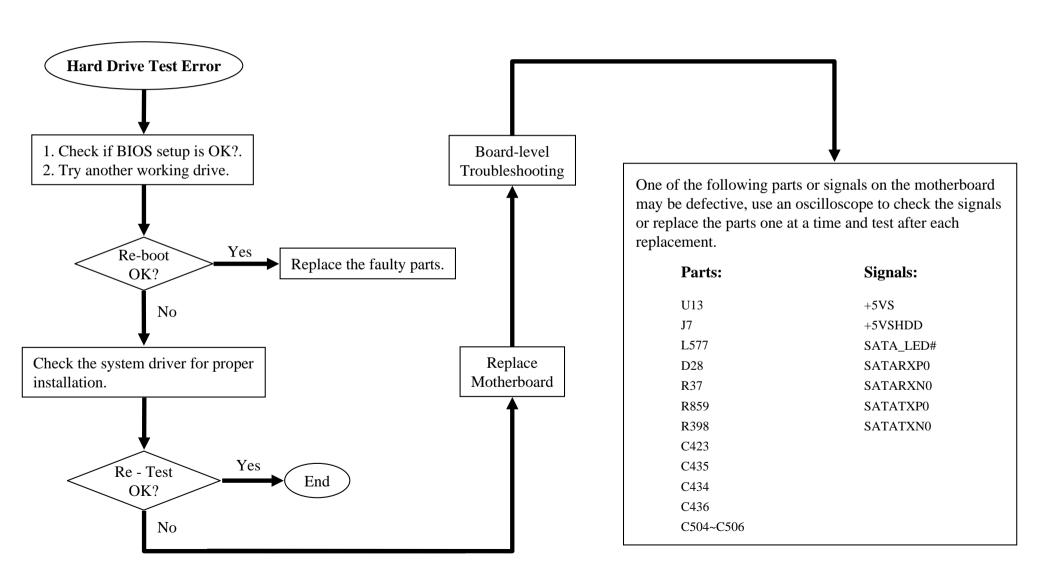

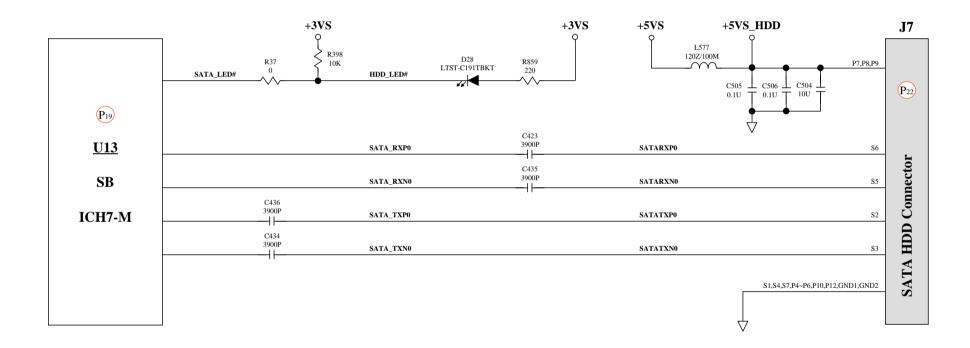

| 8.8 Hard Driver Test Error                    |     |

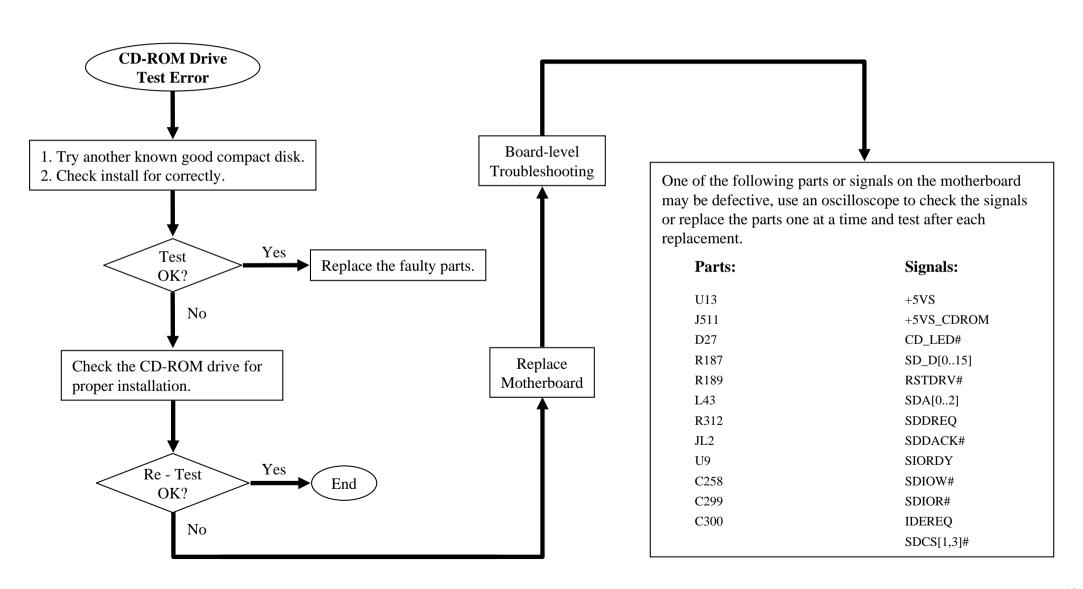

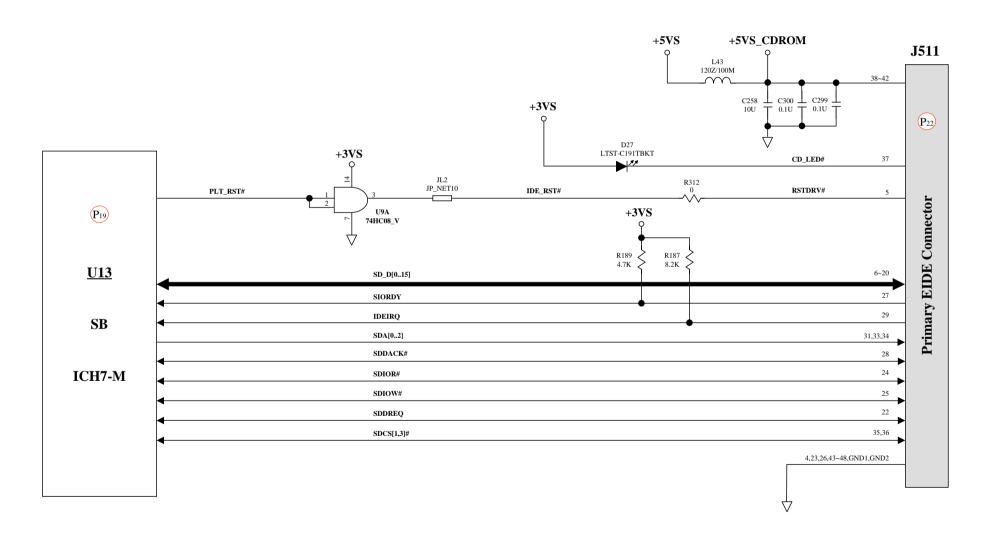

| 8.9 CD-ROM Driver Test Error                  |     |

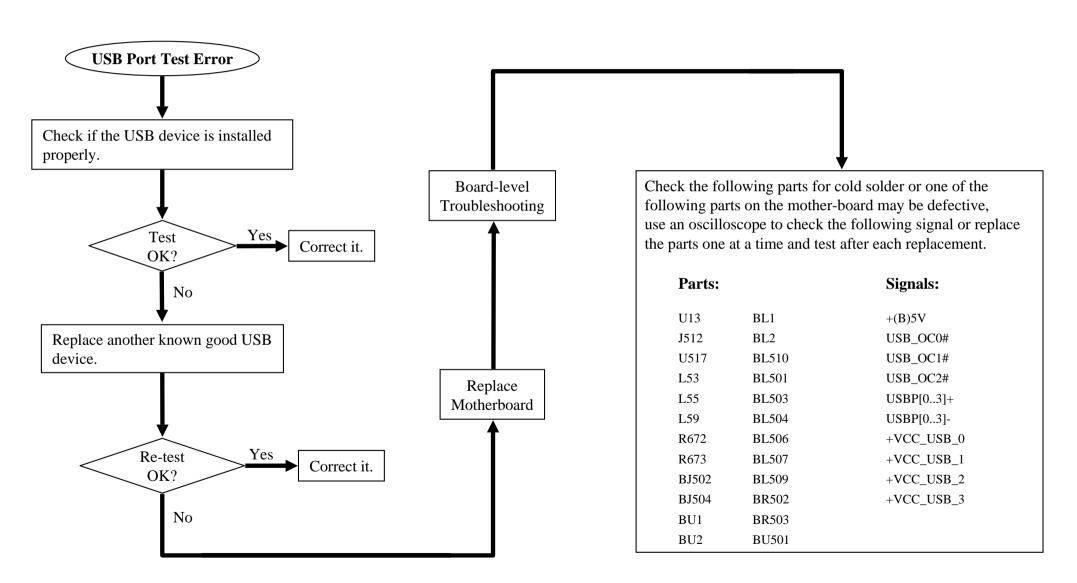

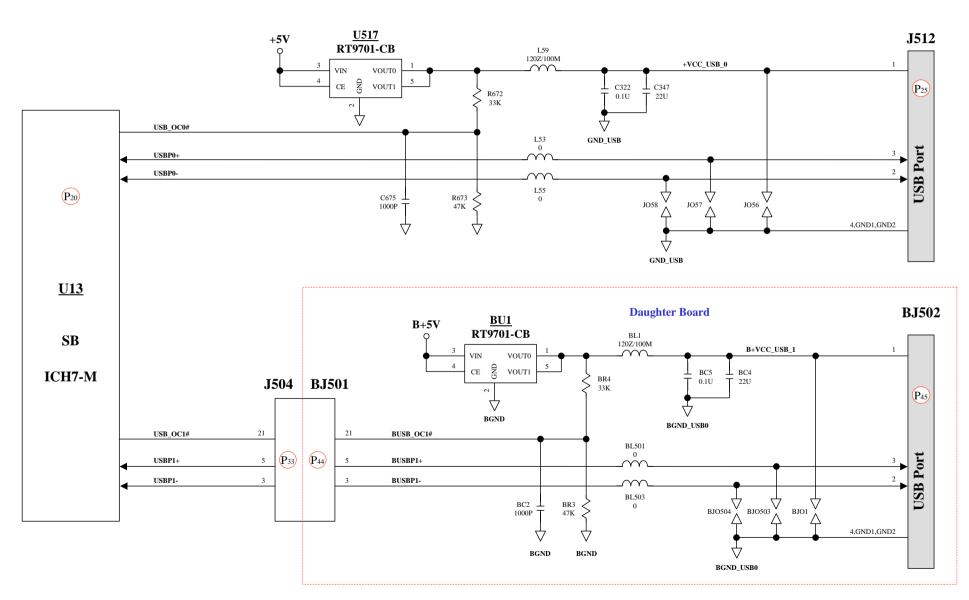

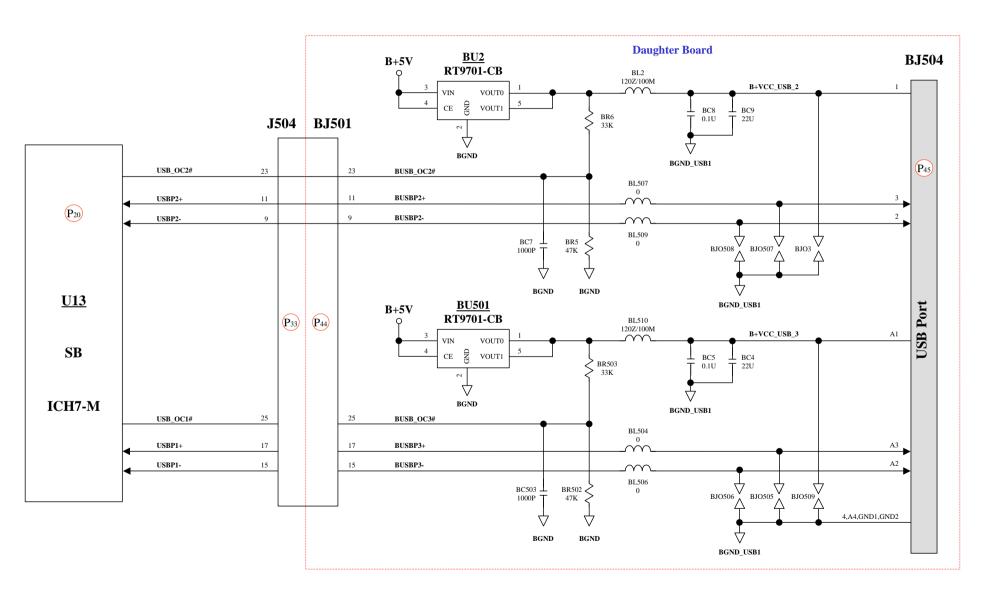

| 8.10 USB Port Test Error                      |     |

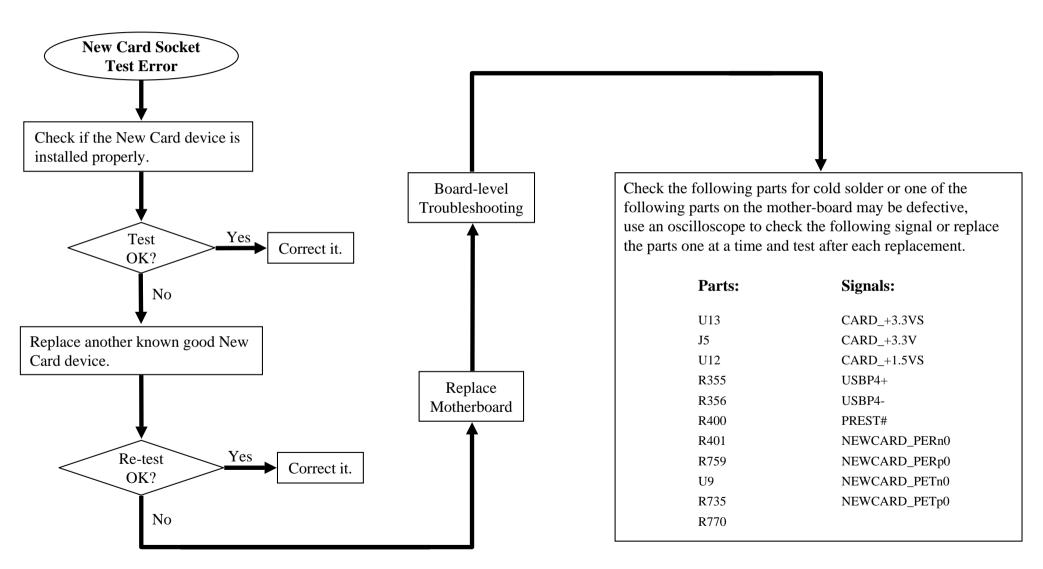

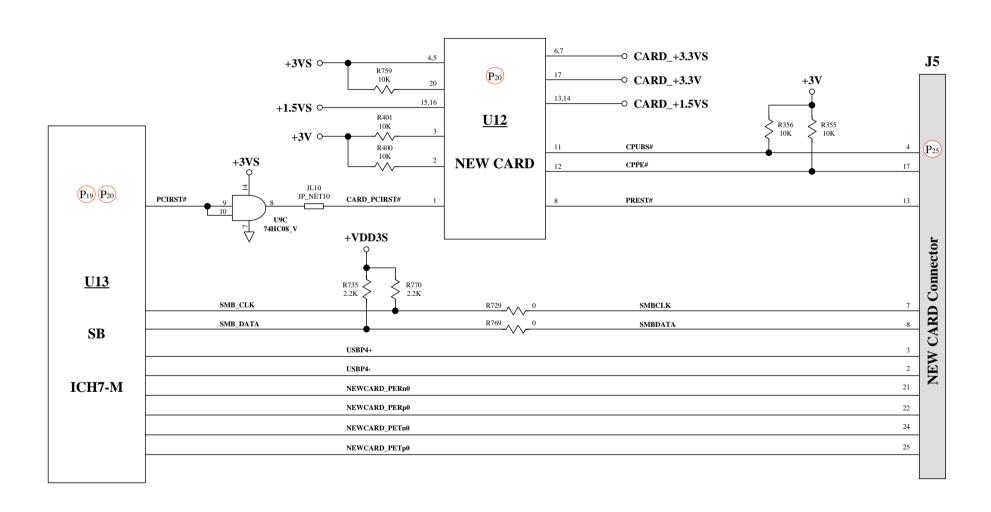

| 8.11 New Card Socket Test Error               |     |

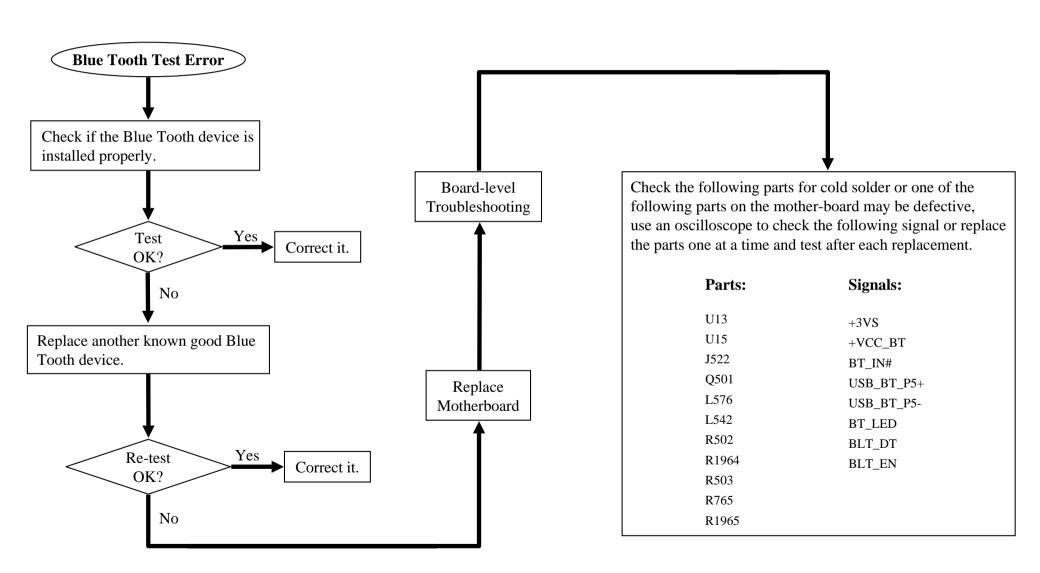

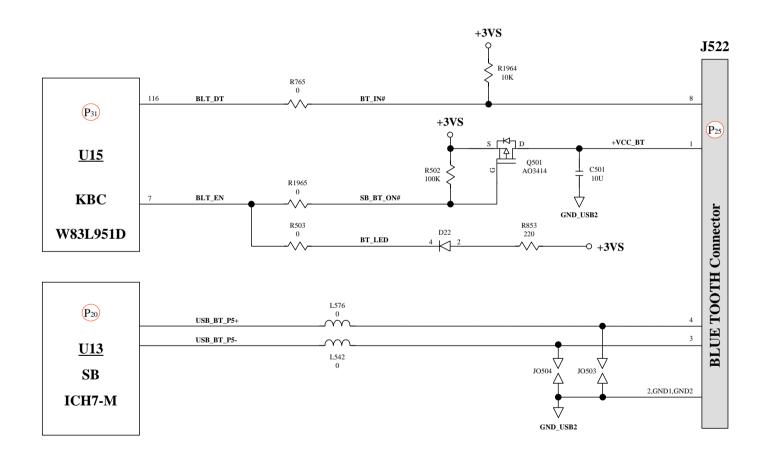

| 8.12 Blue Tooth Test Error                    |     |

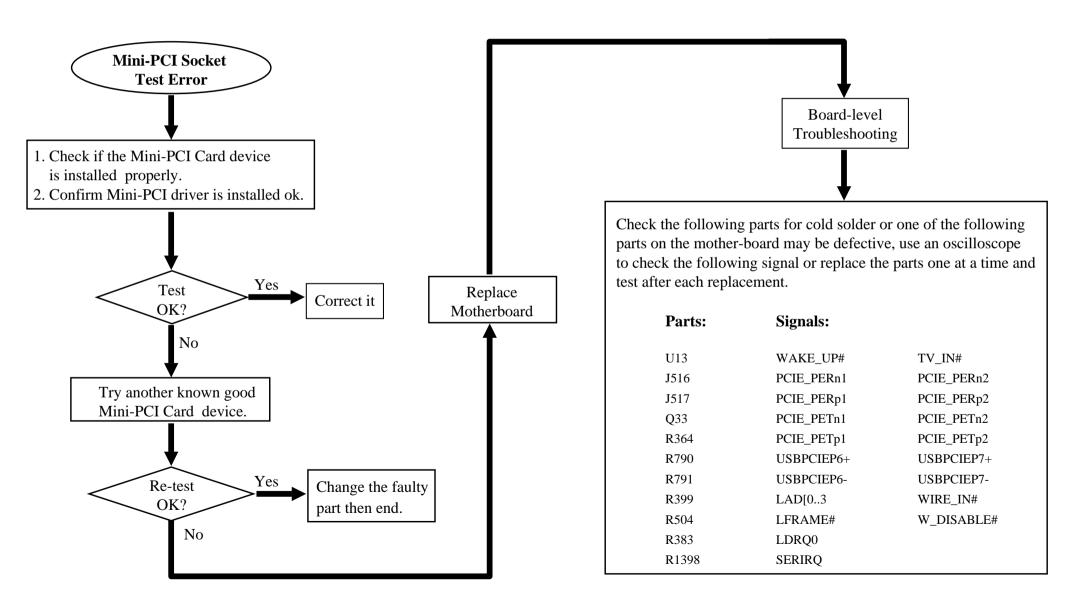

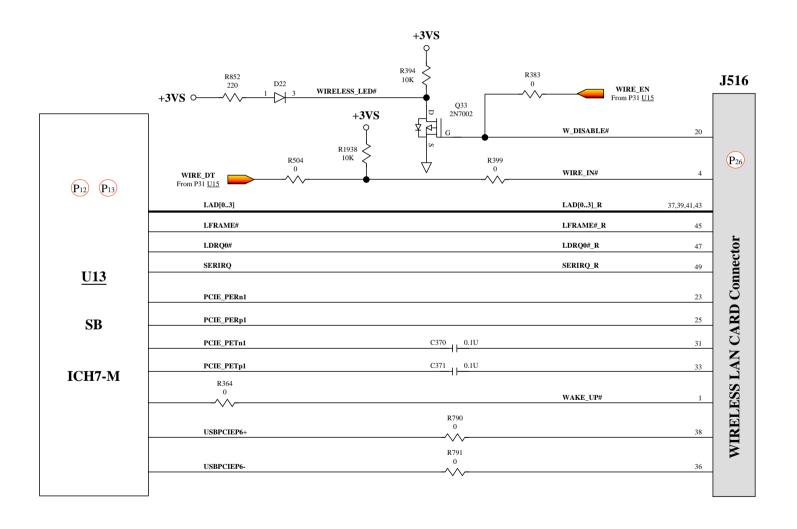

| 8.13 Mini-PCI Socket Test Error               |     |

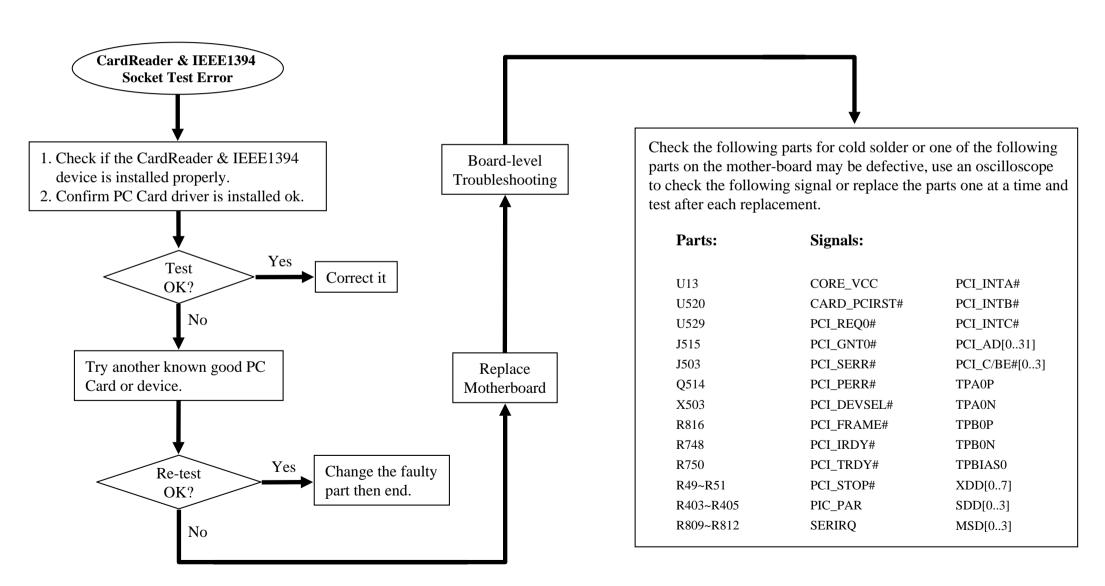

| 8.14 CardReader & IEEE1394 Socket Test Error  |     |

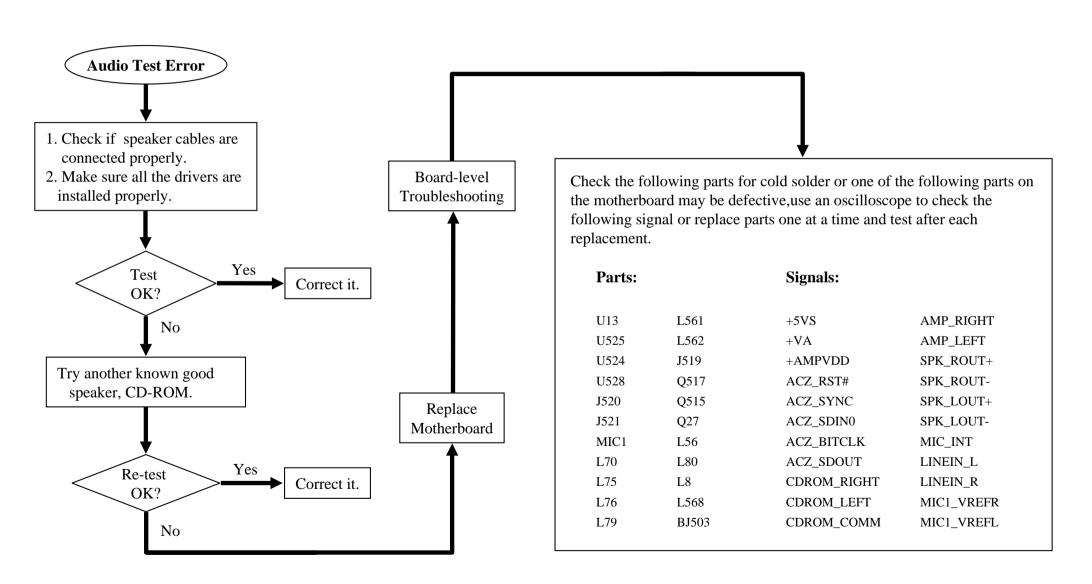

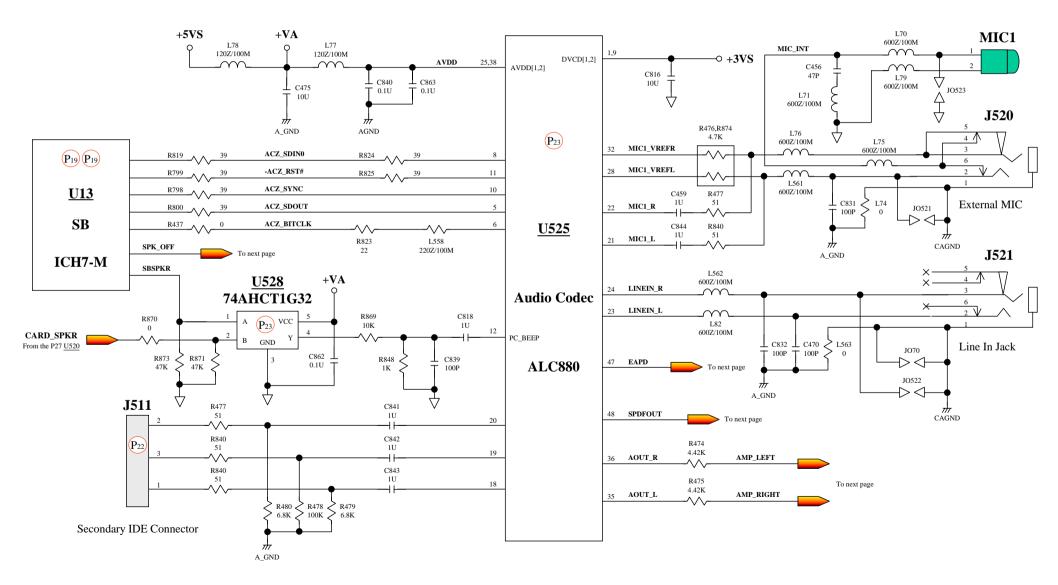

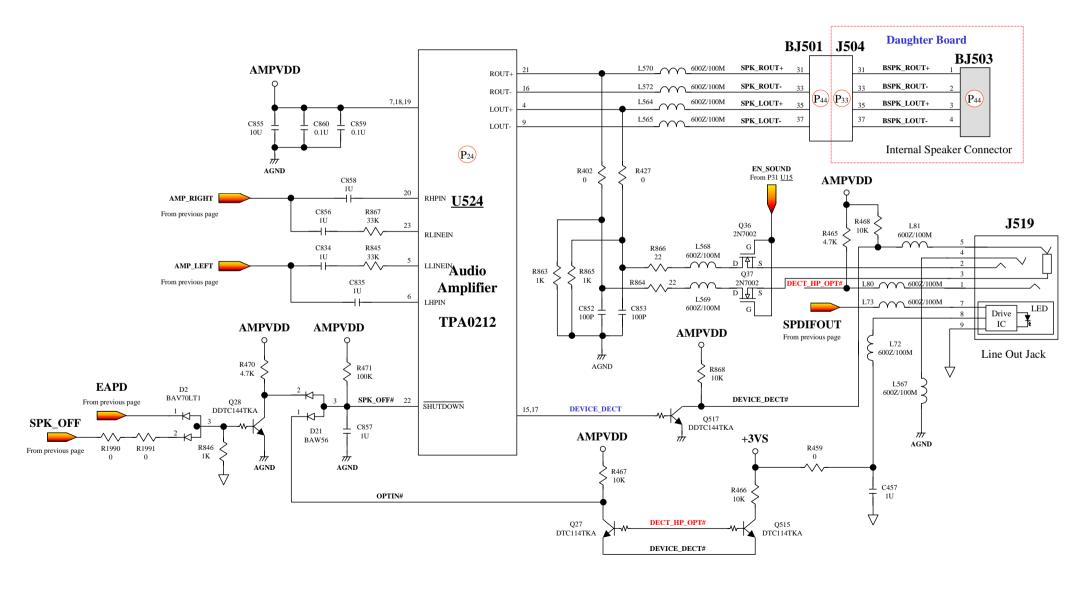

| 8.15 Audio Test Error                         |     |

### **Contents**

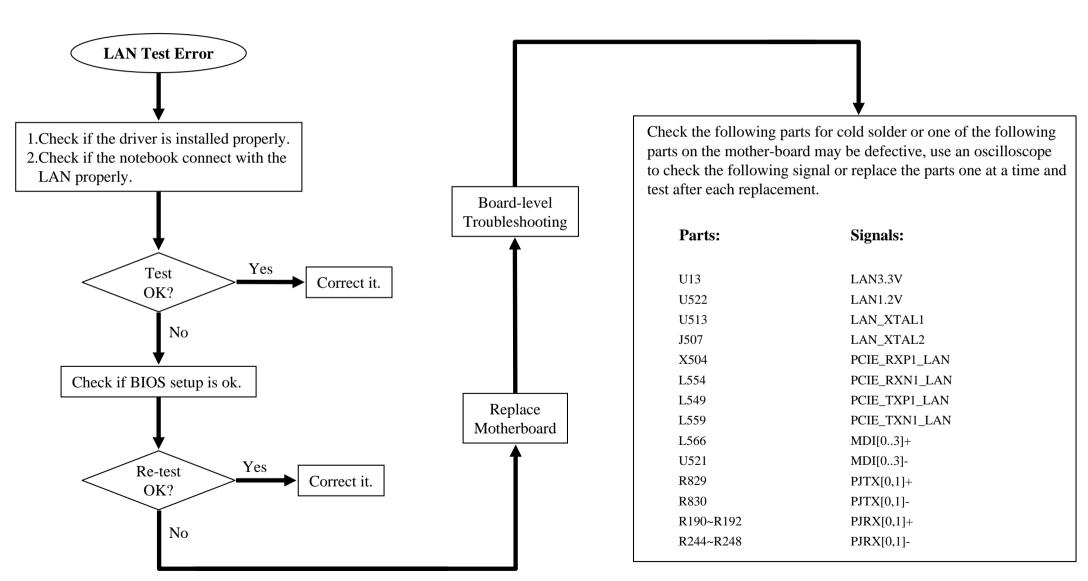

| 8.16 LAN Test Error       | 149 |

|---------------------------|-----|

| 9. Spare Parts List       | 15  |

| 10. System Exploded Views | 163 |

| 11. Reference Material    | 165 |

### 1. Hardware Engineering Specification

### 1.1 Introduction

### 1.1.1 General Description

This document describes the brief introduction for MiTAC 8224 portable notebook computer system.

### 1.1.2 System Overview

The MiTAC 8224 model is designed for Intel Mobile Pentium-M Processor Yonah 533 and 667 FSB.

This system is based on PCI architecture and is fully compatible with IBM PC/AT specification, which has standard hardware peripheral interface. The power management complies with Advanced Configuration and Power Interface. It also provides easy configuration through CMOS setup, which is built in system BIOS software and can be pop-up by pressing F2 key at system start up or warm reset. System also provides icon LEDs to display system status, such as AC Power indicator, Battery Power indicator, Battery status indicator, HDD,CD-ROM, NUM LOCK, CAP LOCK, SCROLL LOCK. It also equipped with GIGA LAN, 56K Fax MODEM, 4 USB port, S-Video and audio line out, SPIDIF, and internal/external microphone function.

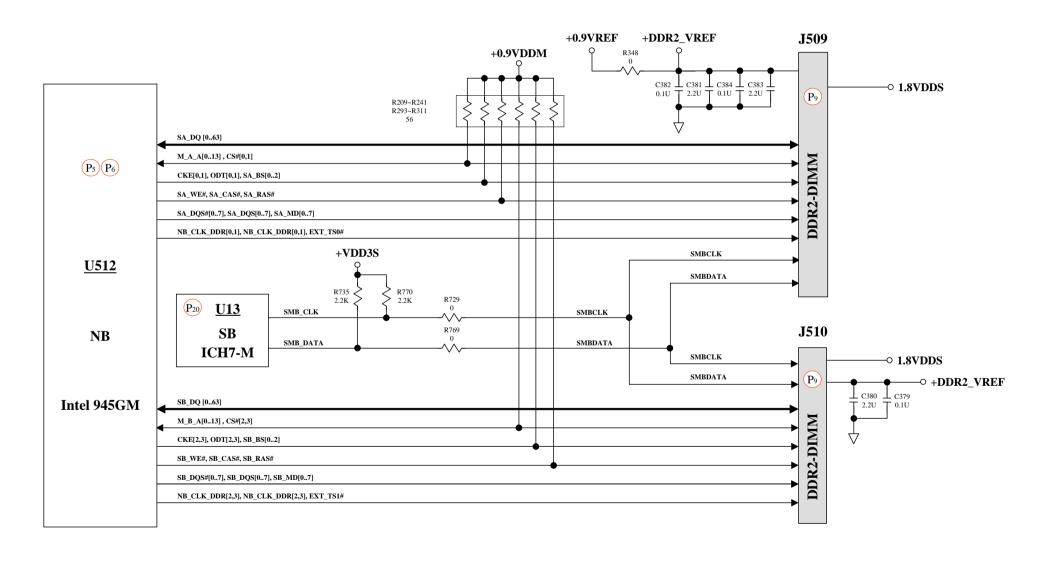

The memory subsystem supports DDR2 SDRAM channels (64-bits wide).

The 945GM MCH Host Memory Controller integrates a high performance host interface for Intel Yonah processor,

a high performance PCI Express interface, a high performance memory controller, Digital Video port (DVOB & DVOC) interface, and Direct Media Interface (DMI) connecting with Intel ICH7-M.

The Intel ICH7-M integrates three Universal Serial Bus 2.0 Host Controllers Interface (UHCI), the Audio Controller with Azalia interface, the Ethernet includes a 32-bit PCI controller, the IDE Master/Slave controllers, the SATA controller and Direct Media Interface technology.

Intel Graphics enhancements includes DVMT 3.0, Zone Rendering 2.0, Quad pixel pipe rendering engine, Pixel Shader 2.0 and 4x Faster Setup Engine.

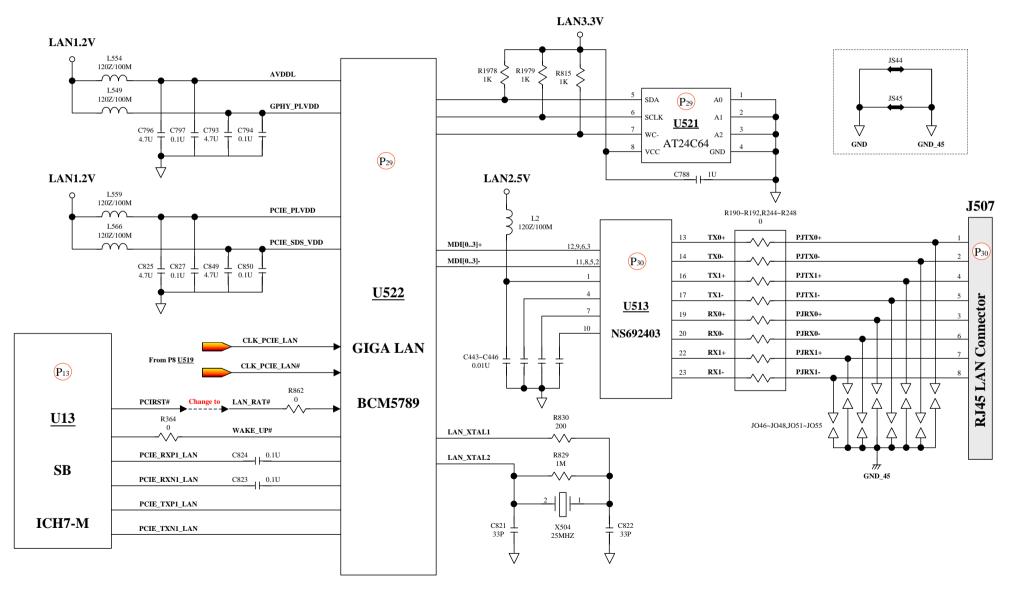

The BCM5789 is a highly integrated, cost-effective single-chip Fast Ethernet controller that provides 32-bit performance, PCI bus master capability, and full compliance with IEEE 802.3u 100Base-T specifications and IEEE 802.3x Full Duplex Flow Control. It also supports the Advanced Configuration Power management Interface (ACPI).

The Texas Instruments PCI8402 controller is an integrated single-socket IEEE 1394 open HCI host controller.and one-port PHY and flash media controller. This high-performance integrated solution provides the latest in IEEE 1394, SD, MMC, Memory Stick/PRO, SmartMedia, and xD technology.

The ALC880 2-Channel High Definition Audio Codec with UAA (Universal Audio Architecture), featuring a 24-bit two-channel DAC and two stereo 20-bit ADCs, are designed for commercial Notebook PC system. The ALC880 provide 2 output channels, along with flexible mixing, mute, and fine gain control functions. Also, supporting 32-bit S/PDIF input and output functions and a sampling rate of up to 96kHz.

The W83L951D is a high performance microcontroller on-chip supporting functions optimized for embedded control. These include ROM, RAM, four types of timers, a serial communication interface, optional I<sup>2</sup>C bus

interface, host interface, A/D converter, D/A converter, I/O ports, and other functions needed in control system configurations, so that compact, high performance systems can be implemented easily.

A full set of software drivers and utilities are available to allow advanced operating systems such as Windows ME, Windows 2000 and Windows XP to take full advantage of the hardware capabilities. Features such as bus mastering IDE, Plug and Play, Advanced Power Management (APM) with application restart, software-controlled power shutdown.

Following chapters will have more detail description for each individual sub-systems and functions.

## 1.1.3 System Parts

| Item                   | Description                                                                                                        |

|------------------------|--------------------------------------------------------------------------------------------------------------------|

| CPU                    | Mobile Pentium-M Processor Yonah 533 and 667 FSB Thermal spec 40 W TDP                                             |

| Core Logic             | Intel 945GM(PM) + ICH7-M chipset                                                                                   |

| System BIOS            | SST49LF004A                                                                                                        |

| Memory                 | DDR2 533 256 MB: Nanya NT256T64UH4A0FN-37B                                                                         |

| HDD                    | SATA: Fujitsu: MHT2060BH, 60 GB<br>PATA: Fujitsu: MHT2060AT+, 60 GB                                                |

| ODD                    | COMBO : Lite-On LSC-2483K or KME-UJDA760                                                                           |

| Display                | 14.1W": AUO B141XG05<br>CHI-MEI N141I1-L02                                                                         |

| Clock Generator        | ICS 9LPR310                                                                                                        |

| Video Control          | Intel 945GM<br>ATI: M56-P with 8 cells 32 MB GDDR2 memory                                                          |

| LAN                    | BCM5787                                                                                                            |

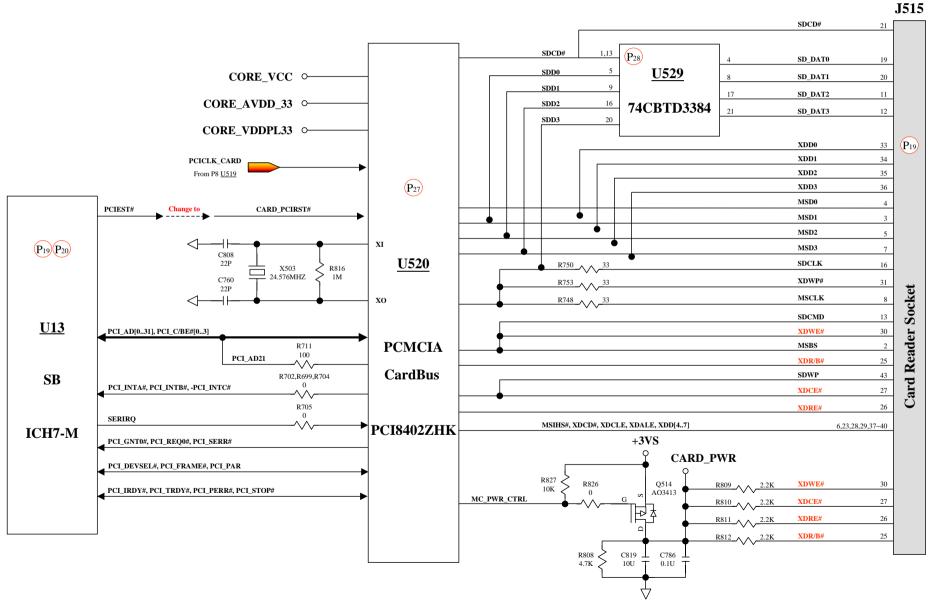

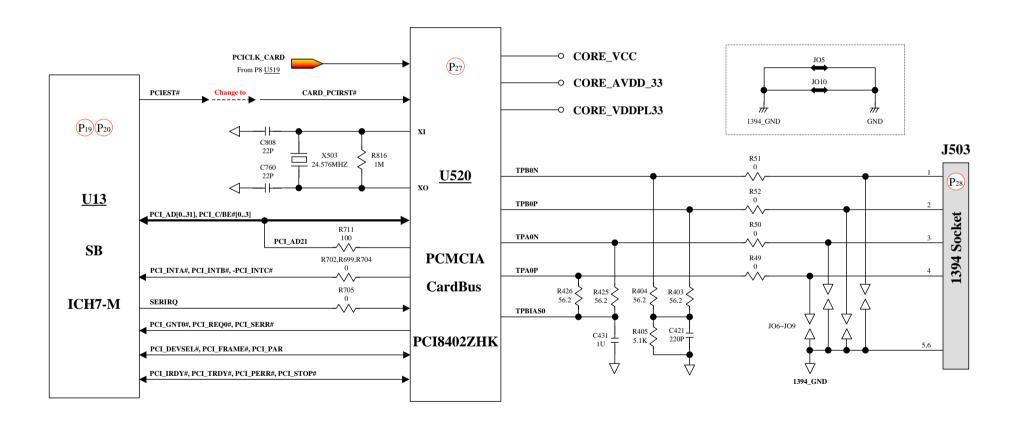

| Card Reader + IEEE1394 | PCI8402ZHK                                                                                                         |

| Audio System           | Azalia CODEC: ALC880                                                                                               |

| Modem                  | 56 Kbps(V.90) Fax Modem(MDC(Azalia I/F)) and 10/100(Reserved for 1000) Base-TX LAN Ekron (10/100) or Vidalia (GbE) |

| Wireless LAN           | Wireless LAN Intel Pro/Wireless 3945ABG(Mini PCI-E Interface IEEE802.11a, b, g)with RF(USB interface)              |

| CIR                    | IRM-2638                                                                                                           |

| USB                    | USB2.0 x 4 (individual)<br>Internal USB: Blue Tooth                                                                |

| TV Tuner Card          | Mini-PCI-E A VerMedia Hybrid TV Tuner Card                                                                         |

| New Card               | Mini-PCI-E interface                                                                                               |

### 1.2 Hardware System

### 1.2.1 Intel Yonah Processors in Micro-FCBGA Package

Intel Yonah Processors with 478 pins Micro-FCBGA package. The Yonah processor is built on Intel's next generation 65 nanometer process technology. Yonah is Intel's first dual core processor for mobile. The following list provides some of the key features on this processor:

- First dual core processor for mobile

- Supports Intel Architecture with Dynamic Execution

- On-die, primary 32 kB instruction cache and 32 kB write-back data cache

- On-die, 2 MB second level cache with Advanced Transfer Cache Architecture

- Data Prefetch Logic

- Streaming SIMD Extensions 2 (SSE2) and Streaming SIMD Extensions 3 (SSE3)

- The Yonah Standard Voltage and Low Voltage processor are offered at 667 MHz FSB

- The Yonah Ultra Low Voltage processor is offered at 533 MHz FSB

- Advanced Power Management features including Enhanced Intel SpeedStep technology

- Digital Thermal Sensor

- Micro-FCPGA and Micro-FCBGA packaging technologies

- Execute Disable Bit support for enhanced security

- Intel Virtualization Technology

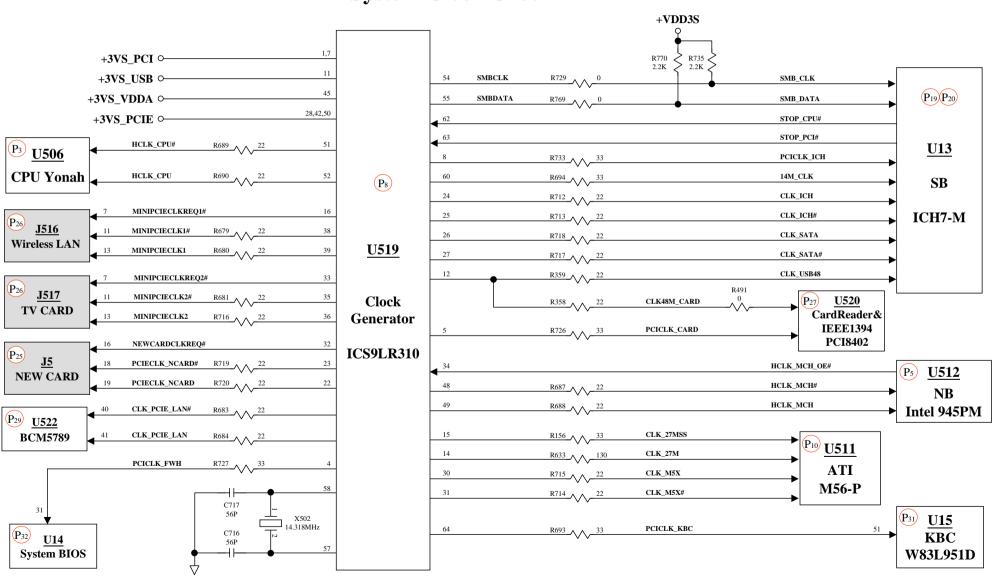

### 1.2.2 Clock Generator

**ICS9LPR310** is a low power CK410M-compliant clock specification. This clock synthesizer provides a single chip solution for next generation P4 Intel processors and Intel chipsets. **ICS9LPR310** is driven with a 14.318MHz crystal.

#### **Output Features:**

- 2 0.7 V differential CPU pairs

- 8 0.7 V differential PCIEX pairs

- 1 0.7 V differential SATA pair

- 1 0.7 V differential LCDCLK/PCIEX selectable pair

- 4 PCI (33 MHz)

- 2 PCICLK\_F, (33 MHz) free-running

- 1 USB, 48 MHz

- 1 DOT 96 MHz/27 MHz selectable pair

- 2 REF, 14.318 MHz

### **\*** Key Specifications:

- CPU outputs cycle-cycle jitter < 85ps

- PCIEX outputs cycle-cycle jitter < 125ps

- SATA outputs cycle-cycle jitter < 125ps

- PCI outputs cycle-cycle jitter < 500ps

- +/- 300ppm frequency accuracy on CPU, PCIEX and SATA clocks

- +/- 100ppm frequency accuracy on USB clocks

#### **Features/Benefits:**

- Supports tight ppm accuracy clocks for Serial-ATA and PCIEX

- Supports programmable spread percentage and frequency

- Uses external 14.318 MHz crystal, external crystal load caps are required for frequency tuning

### 1.2.3 The Mobile Intel 945GM Express Chipset

The Mobile Intel 945GM Express Chipset is designed for use in Intel's next generation mobile platform, code named NAPA.

The Intel 945GM Express Chipset come with the Generation 3.5 Intel Integrated Graphics Engine, and the Intel Graphics Media Accelerator (GMA) 950, providing enhanced graphics support over the previous generation (G)MCH's.

The (G)MCH manages the flow of information between the four following primary interfaces:

- FSB

- System Memory Interface

- Graphics Interface

- DMI

The (G)MCH can also be enabled to support external graphics, using the x16 PCI Express Graphics attch port. When external graphics is enabled, the internal graphics port are inactive.

#### **Features**

- Processor Support

- All Yonah variants

- Merom support

- 533 MHz and 667MHz Front Side Bus (FSB) support

- Source synchronous double-pumped (2x) Address

- Source synchronous quad-pumped (4x) Data

- Other key features are:

- -- Support for DBI (Data Bus Inversion)

- -- Support for MSI (Message Signaled Interrupt)

- -- 32-bit interface to address up to 4 GB of memory

- -- A 12 deep In-Order Queue to pipeline FSB commands

- -- GTL+ bus driver with integrated GTL termination resistors

#### Memory System

- Support Single/Dual Channel DDR2 SDRAM

- Maximum Memory supported 2 GB

- 64 bit wide per channel

- Three Memory Channel Configurations supported

- -- Single Channel

- -- Dual Channel Symmetric

- -- Dual Channel Asymmetric

- One SO-DIMM connector per channel

- Support for DDR2 at 400MHz, 533MHz and 667MHz

- 256Mb, 512Mb and 1 Gb Memory Technologies supported

- Support for x8 and x16 devices

- Maximum Memory supported: 2 GB

- Support for DDR2 On-Die Termination (ODT)

- Supports Partial Writes to memory using Data Mask signals (DM)

- Intel Rapid Memory Power Management

- Dynamic row power-down

- No support for Fast Chip Select mode

- Support for 2N timings only

### Discrete Graphics using PCI Express

- One 16-lane (x16) PCI Express port for external PCI Express Based graphics card

- Fully compliant to the PCI Express Base Specification revision 1.0a. base PCI Express frequency of 2.5 GHz only

- Raw bit-rate on the data pins of 2.5Gb/s, resulting in a real bandwidth per pair of 250 MB/s given the 8/10 encoding used to transmit data across this interface

- Maximum theoretical realized bandwidth on interface of 4 GB/s in each direction simultaneously, for an aggregate of 8 GB/s when x16

- 100 MHz differential reference clock (shared by PCI Express Gfx and DMI)

- STP-AGP/AGP\_BUSY Protocol equivalent for PCI Express based attach is via credit based PCI Express mecanism

- PCI Express power management support: L0s, L1, L2/L3 Ready, L3

- Lane# 0 only for signaling and detection of exit from L0s and L1

- Hierarchical PCI-compliant configuration mechanism for downstream devices (i.e., normal PCI 2.2 Configuration space as a PCI-to-PCI Bridge)

- PCI Express Extended Configuration Space. The first 256 bytes of configuration space aliases directly to the PCI Compatibility configuration space. The remaining portion of the fixed 4KB block of memory-mapped space above that (starting at 100h) is known as extended configuration space

- PCI Express Enhanced Addressing Mechanism. Accessing the device configuration space in a flat memory mapped fashion

- Automatic discovery, negotiation, and training of link out of reset

- Supports traditional PCI style traffic (asynchronous snooped, PCI ordering)

- Supports traditional AGP style traffic (asynchronous non-snooped, PCI-X Relaxed ordering)

- Support for peer segment destination write traffic (no peer-to-peer read traffic) in Virtual Channel 0 only

- APIC and MSI interrupt messaging support. Will send Intel-defined "End Of Interrupt" broadcast message when initiated by the CPU

- Support for Isochronous non-snooped traffic through a dedicated Virtual Channel

- Downstream Lock Cycles(including Split Locks)

- Automatic clock extraction and phase correction at the receiver

#### Internal Graphics

- Intel Gen 3.5 Integrated Graphics Engine

- 250 MHz core rendor clock at 1.05V core voltage

- Supports TV-Out, LVDS, CRT and SDVO

- Intel Dual Frequency Graphics Technology

- Intel Dynamic Video Memory Technology (DVMT 3.0)

- Intel Smart 2D Display Technology

- Intel Display Power Saving Technology 2.0

- Video Capture via x1 concurrent PCIE port

- Higher Performance MPEG-2 Decoding

- Hardware Acceleration for VLD / iDCT

- 4x pixel rate HWMC

- DX 9.1

- Hardware Motion Compensation

- Intermediate Z in Classic Rendering

#### Analog CRT

- Integrated 400 MHz RAMDAC

- Analog Monitor Support up to QXGA (2048 x 1536)

- Support for CRT Hot Plug

#### Dual Channel LVD

- Panel support up to UXGA (1600 x 1200)

- 25-112 MHz single / dual channel

- -- Single channel LVDS interface support: 1 x 18 bpp

- -- Dual channels LVDS interface support: 2 x 18 bpp panel support up to UXGA (1600 x 1200)

- -- TFT panel type supported

- Pixel Dithering for 18 bit TFT panel to emulate 24 bpp true color displays

- Panel Fitting. Panning, and Center Mode Supported

- CPIS 1.5 compliant

- Spread spertrum clocking supported

- Panel Power Sequencing support

- Integrated PWM interface for LCD backlight inberter control

#### \* TV - OUT

- Three integrated 10 bit DACS

- Macro Vision support

- Overscaling

- NTSC / PAL

- Component, S-Video and Composite Output interfaces

- HDTV support

- -- Single channel LVDS interface support: 1 x 18 bpp

#### DMI

- Chip-to-chip interface between (G)MCH and Intel 82801GBM (ICH7M)

- Configurable as x2 or x4 DMI lanes

- 2 GB/s (1 GB/s each direction) point-to-point interface to Intel 82801GBM

- 32 bit downstream address

- Direct Media Interface asynchronously coupled to core

- Supports 3 Virtual Channels for traffic class performance differentiation

- Supports both snooped and non-snooped traffic

- Supports isochronous non-snooped traffic

- Supports legacy snooped isochronous traffic

- Supports the following traffic types to or from Intel 82801GBM

- Peer write traffic between DMI and PCI Express Graphics port

- DMI-to-DRAM

- DMI-to-CPU (FSB Interrupts or MSIs only)

- CPU-to-DMI

- Messaging in both directions, including Intel Vendor-specific messages

- Supports Power Management state change messages

- APIC and MSI interrupt messaging support

- Supports SMI, SCI and SERR error indication

- Legacy support for ISA regime protocol (PHOLD/PHOLDA) required for parallel port DMA, floppy drive, and LPC bus masters

### 1.2.4 I/O Controller Hub: INTEL ICH7-M

The ICH7 provides extensive I/O support. Functions and capabilities include:

- PCI Express Base Specification, Revision 1.0a support

- PCI Local Bus Specification, Revision 2.3 support for 33 MHz PCI operations (supports up to six Req/Gnt pairs)

- ACPI Power Management Logic Support

- Enhanced DMA controller, interrupt controller, and timer functions

- Integrated Serial ATA host controller with independent DMA operation on four ports and AHCI (ICH7R only)support

- USB host interface with support for eight USB ports; four UHCI host controllers; one EHCI high-speed USB 2.0 Host controller

- Integrated LAN controller

- System Management Bus (SMbus) Specification, Version 2.0 with additional support for I<sup>2</sup>C devices

- Supports Audio Codec '97, Revision 2.3 Specification (a.k.a, AC '97 Component Specification, Revision 2.3) which provides a link for Audio and Telephony codecs (up to 7 channels)

- Supports Intel High Definition Audio

- Supports Intel Matrix Storage Technology (ICH7R only)

- Supports Intel Active Management Technology

- Low Pin Count (LPC) interface

- Firmware Hub (FWH) interface support

- Serial Peripheral Interface (SPI) support

### 1.2.5 VGA Controller: ATI M56-P

The M52-P is based on PCI Express technology and leverages a brand new graphics architecture. Based on 90nm micron process technology, the M52-P will deliver a 16-lane PCI Express bus interface and lead-free ASIC.

#### **Features**

#### Processor / Host Bus Support

- Support for Microsoft® DirectX® 9.0 programmable vertex and pixel shaders in hardware.

- Shader model 3.0 vertex and pixel shader support:

- Full speed 32-bit floating point processing

- High dynamic range rendering with floating point blending support

- High performance dynamic branching and flow control

- Complete feature set also supported in OpenGL® 2.0.

### Anti-Aliasing and Anisotropic Filtering

- 2x/4x/6x Anti-Aliasing modes

- Sparse multi-sample algorithm with gamma correction, programmable sample patterns, and centroid sampling

- Lossless Color Compression (up to 6:1) at all resolutions, including widescreen HDTV resolutions

- Temporal Anti-Aliasing

- 2x/4x/8x/16x Anisotropic Filtering modes

- Up to 128-tap texture filtering

- Adaptive algorithm with performance and quality options

### **❖** 3Dc+™ — Advanced Texture Compression

- High quality 4:1 compression for normal maps and luminance maps

- Works with any single-channel or two-channel data format

#### **⋄** Next-Generation HYPER Z<sup>™</sup> Technology

- Hierarchical Z-Buffer with Early Z Test

- Lossless Z-Buffer Compression (up to 48:1)

- Fast Z-Buffer Clear

- Z Cache optimized for real-time shadow rendering

- Optimized for performance at high display resolutions, including widescreen HDTV resolutions

#### **\*** High Performance Memory Support

Support for DDR1 and DDR2 SDRAM/SGRAM, and GDDR3 SDRAM (except M56-P)

#### Programmable Video Processing Engine

- Seamless integration of pixel shaders with video in real time

- FULLSTREAM<sup>TM</sup> video de-blocking technology for Real, DivX, and WMV9 formats

- VIDEOSOAP<sup>TM</sup> noise removal filtering for captured video

- MPEG1/2/4 decode and encode acceleration

- DXVA Support

- Hardware Motion Compensation, iDCT, DCT and color space conversion

- All-format DTV/HDTV decoding

- YPrPb component output for direct drive of HDTV displays

- Adaptive Per-Pixel De-Interlacing and Frame Rate Conversion (temporal filtering)

- Dual integrated display controllers

- Dual integrated 10 bit per channel 400 MHz DACs

- Integrated 165 MHz TMDS transmitter (DVI 1.0 / HDMI compliant and HDCP ready)

- Additional external TMDS support for dual-link DVI

- Integrated TV Output support up to 1024x768 resolution

### 1.2.6 AZALIA AUDIO SYSTEM: ALC880

ALC880 provides 7.1 channels of outputs and multiple stereo inputs, along with flexible mixing, mute and finer gain control functions to provide a complete integrated audio solution for PCs. Also the highest 192KHz sample rate DACs and Realtek proprietary hardware content protection are applicable for DVD Audio, which only implemented in high end consumer electronics, now is achieved by PCs with ALC880 inside. ALC880 is also the one and only High Definition Audio Codec integrating three pairs of stereo ADCs which can support microphone array with AEC (Acoustic Echo Cancellation), BF (Beam Forming) and NS (Noise Suppression) technology simultaneously to significantly improve recording quality for conference call. With this unique feature (3 pairs of Stereo ADCs), ALC880 can perform the ultimate performance of HAD like using S/PDIF to output analog data or multiple recording application.

#### Features

- High performance DACs with 95dB S/N ratio

- Meets performance requirements for audio on PC2001 systems

- 8 channels of DAC support 16/20/24-bit PCM format for 7.1 audio solution

- 3 stereo ADCs support 16/20-bit PCM format, two for microphone array, one for legacy mixer recording

- Supports 44.1K/48K/96K/192KHz DAC sample rate

- All ADCs support 44.1K/48K/96K sample rate

- Applicable for 4ch/192KHz and 6ch/96KHz DVD-Audio solution

- Up to 4 channels of microphone input are supported for AEC/BF application

- Support Power Off CD function

- Support external PCBEEP input and built in BEEP generator

- PCBEEP Pass-Through when link is in RESET state

- Software selectable 2.5V/3.75V VREFOUT

- Default 6 VREFOUTs are supported, additional 4 VREFOUTs are capable by sharing un-used analog I/O pins

- 2 jack detection pins each supports up to 4 jacks plugging can be detected

- 16/20/24-bit S/PDIF-OUT supports 44.1K/48K/96KHz sample rate

- 16/20/24-bit S/PDIF-IN supports 44.1K/48K/96KHz sample rate

- Optional EPAD (External Amplifier Power Down) is supported

- Power support: Digital: 3.3V; Analog: 3.3V/5.0V

- Power management and enhanced power saving features

- 48-pin LQFP package is compatible with AC'97

- Reserve analog mixer architecture is backward compatible with AC'97

- -64dB ~ +30dB with 1dB resolution of mixer gain to achieve finer volume control

- Impedance sensing capability for each re-tasking jack

- All analog jacks are stereo input and output re-tasking for analog plug & play

- Built in headphone amplifier for each re-tasking jack

- Support external volume knob control

- Support 2 GPIO (General Purpose Input/Output) for customized application

- Hardware content protection for DVD-Audio supporting

### 1.2.7 MDC: Azalia MDC Modem Card (MDC56AZS2)

#### Features

- AC'97/MC'97 2.2 compliant

- MDC Modem support current sense, whenever the current on the line exceeds approximately 150mA, and should immediately go back on hook

- ITU-T V.92 PCM Upstream and V.90 data rates with auto0fallback to V.34, V.32ter V.32 bis and fallbacks

- Virtual Com port with a through put of up to 460.8Kbps

- V.42 bis/MNP 5 data compression

- FAX: Send and receive rates up to 14.4kbps, V.17, V.29, V.27ter

- Hayes AT Command set

- Supports V.42 error correction and V.44, V.42bis/MNP5 data compression

- FAX capabilities: ITU-T V.17, V.29, V.27ter, V.21 Ch2 and TIA/EIA 578 Class1 FAX

- Modem Support Wake up on Ring

### 1.2.8 System Flash Memory (BIOS)

- Firmware Hub for Intel® 810, 810E, 815, 815E,815EP, 820, 840, 850 Chipsets

- Flexible Erase Capability

- -- Uniform 4 KByte Sectors

- -- Uniform 16 KByte overlay blocks for SST49LF002A

- -- Uniform 64 KByte overlay blocks for SST49LF004A

- -- Top boot block protection

- -- 16 KByte for SST49LF002A

- -- 64 KByte for SST49LF004A

- -- Chip-Erase for PP Mode

- Single 3.0-3.6V Read and Write Operations

- Superior Reliability

- Firmware Hub Hardware Interface Mode

- -- 5-signal communication interface supporting byte Read and Write

- -- 33 MHz clock frequency operation

- -- WP# and TBL# pins provide hardware write protect for entire chip and/or top Boot Block

- -- Block Locking Register for all blocks

- -- Standard SDP Command Set

- -- Data# Polling and Toggle Bit for End-of-Write detection

- -- 5 GPI pins for system design flexibility

- -- 4 ID pins for multi-chip selection

### 1.2.9 Memory System

- **128MB**, 256MB, 512MB, 1GB (x64) 200-Pin DDR2 SDRAM SODIMMs

- JEDEC-standard 200-pin, small-outline, dual in-line memory module (SODIMM)

- VDD=+1.8V±0.1V, VDDQ=+1.8V±0.1V

- JEDEC standard 1.8V I/O (SSTL\_18-compatible)

- Differential data strobe (DQS,DQS#) option

- Four-bit prefetch architecture

- Differential clock input (CK,CK#)

- Command entered on each rising CK edge

- DQS edge-aligned with data for Reads

- DQS center-aligned with data for Writes

- Duplicate output strobe (RDQS) option for x8 configuration

- DLL to align DQ and DQS transitions with CK

- Four internal banks for concurrent operation

- Data mask (DM) for masking write data

- Programmable CAS Latency (CL): 2,3,4 and 5

- Posted CAS additive latency (AL): 0,1,2,3 and 4

- Write latency = Read latency -1<sup>t</sup>CK

- Programmable burst lengths: 4 or 8

- Read burst interrupt supported by another READ

- Write burst interrupt supported by another WRITE

- Adjustable data output drive strength

- Concurrent auto precharge option is supported

- Auto Refresh (CBS) and Self Refresh Mode

- 64ms, 8,192-cycle refresh

- Off-chip drive (OCD) impedance calibration

- On-die termination (ODT)

### 1.2.10 GIGALAN – BCM5787

The BCM5787 is a seventh generation 10/100/1000BASE-T Ethernet LAN controller solution for high-performance network applications. The device combines a triple-speed IEEE 802.3 compliant Media Access Controller (MAC) with a triple-speed Ethernet transceiver, 1x PCI-E bus interface, and on-chip buffer memory in a single device. The device is fabricated in a 1.2V CMOS process providing a low-power system solution.

#### Features

- Integrated 10/100/1000BASE-T transceiver

- Automatic MDI crossover function

- PCI-E v1.0a

- 10/100/1000BASE-T full/half-duplex MAC

- Wake on LAN support meeting the ACPI requirements

- Statistics for SNMP MIB II, Ethernet-like MIB, and Ethernet MIB (802.3z, clause 30)

- Serial EEPROM or serial flash support

- JTAG support

- 196-FBGA package

### 1.2.11 Keyboard System: Winbond W83L951DG

The Winbond mobile keyboard and embedded controller W83L951D/F architecture consists of a Turbo-8051 core logic controller and surrounded by various components, 2K+256 bytes of RAM, 64K on-chip FLASH, LPC host interface, 13 general purpose I/O port with 24 external interrupt source, 4 timers, 1 serial port, 2 SMBus interface for master mode, 3 PS/2 port, two 8-bits and two 16-bits PWM channels, 2 D-A and 8 A-D converters, 1 Consumer Infrared Communications Receiver, 2 Fan Tachometer, 1 Real Time Clock Generator, and Matrix Interface. The part number with an affix of "G" is the Lead-free package product.

### Core logic

- 8-bit Turbo 8052 Microprocessor Code based, Speed up to 24MHz

- 256 bytes Internal RAM

- 64K bytes Embedded Programmable Flash Memory

2K bytes External SRAM

#### Host interface

- Software Optional with LPC Interface

- Primary Programmable I/O Address Communication Port in LPC Mode

- Support SERIRQ in LPC Interface

- Support Hardware Fast Gate A20 and KBRST

- Support Port 92h

#### SMBus

Support 2 SMBus Interface support Master Mode

#### Timers

- Support Four Timer Signal with Three Pre-scalars

- Timer 1 and 2 Shard the Same Pre-scalar and are Free-Running Only

- Timer X and Y Have Individual Pre-scalar and Support up to Four Control Modes, Free

- Running, Pulse Output, Event Counter and Pulse Width Measurement

#### PWM

- Support Four PWM Channels

- PWM 0 and 1 are 8-bits and Programmable Frequency from 62Hz to 7.5 KHz

- PWM 2 and 3 are 16-bits and Programmable Frequency from 6Hz to 3MHz

#### Fan Tachometer

Support two Fan Tachometer Inputs

#### A/D Converter

- Firmware Programmable Optional with 10-bite or 8-bit Resolution

- Support Eight Channels

#### D/A Converter

- 8-bit Resolution

- Support Two Channels

#### **❖** PS2

- Support Three Hardware PS2 Channels

- Optional PS2 Clock Inhibit by Hardware or Firmware

### **\*** Keyboard Controller

Support 16\*8 Keyboard Matrix-scan, Expanding to 18\*8 and 20\*8

#### GPIO

Support 104 Useful GPIO Pins Totally and Bit–addressable to Facility Firmware Coding

#### FLASH

• Support External On-Board 64K Flash via Matrix Interface (GP0, 1, 3)

#### CIR

Support Decoding for the NEC Consumer IR Remote Control Format

#### \* RTC

Real Time Clock Generator with 32.768 KHz Input

#### \* ACPI

- Support ACPI Appliance

- Secondary Programmable I/O Address Communication Port in LPC Mode

### Package

128 Pin QFP and 128 Pin LQFP Package Options

### 1.2.12 Hard Disk Drive

8224 can support SATA or PATA HDD by equipped different HDD transition board.

#### SATA HDD

The SATA function in the ICH7 has dual modes of operation to support different operating system conditions. In the case of Native IDE enabled operating systems, the ICH7 has separate PCI functions for serial and parallel ATA ("enhanced mode"). To support legacy operating systems, there is only one PCI function for both the serial and

parallel ATA ports if functionality from both SATA and PATA devices is desired ("combined mode"). SATA interface transfer rates are independent of UDMA mode settings. SATA interface transfer rates will operate at the bus's maximum speed, regardless of the UDMA mode reported by the SATA device or the system BIOS.

- -- Up-to 150MB/sec bus speed (Serial ATA Generation 1)

- -- Compliant with Serial ATA 1.0a Specification and Serial ATA 2 Extensions 1.0

- -- Supports 48bit-LBA addressing

- -- Supports Native DMA Queued command (First party DMA queued)

- -- Also supports Legacy DMA Queued command

- -- Supports Staggered Spin-Up function

- -- Supports Hot-Plug features

- -- Supports Serial ATA power management (Host initiated Partial/Slumber)

#### **❖ IDE HDD**

The ICH7 IDE controller features one set of interface signals that can be enabled, tri-stated or driven low. The IDE interfaces of the ICH7 can support several types of data transfers:

- -- Programmed I/O (PIO): processor is in control of the data transfer

- -- 8237 style DMA: DMA protocol that resembles the DMA on the ISA bus, although it does not use the 8237 in the ICH7. This protocol off loads the processor from moving data. This allows higher transfer rate of up to 16MB/s

- -- Ultra ATA/33/66/100: DMA protocol that redefines signals on the IDE cable to allow both host and target throttling of data and transfer rates of up to 33/66/100 MB/s

## 1.2.13 CIR

The TSOP62.. - series are miniaturized SMD-IR Receiver Modules for infrared remote control systems. PIN diode and preamplifier are assembled on lead frame, the epoxy package is designed as IR filter. The demodulated output signal can directly be decoded by a microprocessor. TSOP62.. is the standard IR remote control SMD-Receiver series, supporting all major transmission codes.

#### **Features**

#### Photo detector and preamplifier in onepackage

- Internal filter for PCM frequency

- Continuous data transmission possible

- TTL and CMOS compatibility

- Output active low

- Low power consumption

- High immunity against ambient light

- Low power consumption

- Lead (Pb)-free component

- Component in accordance to RoHS 2002/95/EC and WEEE 2002/96/EC

## 1.2.14 Card Reader & IEEE 1394 – PCI8402ZHK

The PCI8402 controller is a four-function PCI controller compliant with *PCI Local Bus Specification*, It is 216 ball PBGA package.

Function 0 is a dummy PC Card controller function. The PC Card socket is non-functional and the pins associated with the PC card socket may be left unconnected. The function is required for device enumeration and is provided for BIOS compatibility with existing devices. The PC Card function may be hidden from the OS by the BIOS.

Function 1 of the PCI8402 controller is compatible with IEEE Std 1394a-2000 and the latest *1394 Open Host Controller Interface Specification*. The chip provides the IEEE1394 link and 1-port PHY function and is compatible with data rates of 100, 200, and 400 Mbits per second. Deep FIFOs are provided to buffer 1394 data and accommodate large host bus latencies. The PCI8402 controller provides physical write posting and a highly tuned physical data path for SBP-2 performance.

Function 2 of the PCI8402 controller is a PCI-based Flash Media controller that supports Memory Stick, Memory Stick-Pro, SmartMedia, xD, SD, and MMC cards. This function controls communication with these Flash Media cards through a dedicated Flash Media socket. In addition, this function includes DMA capabilities for improved Flash Media performance.

Function 3 of the PCI8402 controller is a PCI-based SD host controller that supports MMC, SD, and SDIO cards. This function controls communication with these Flash Media cards through a dedicated Flash Media socket. In addition, this function is compliant with the *SD Host Controller Standard Specification* and includes both DMA capabilities and support for SD suspend/resume.

## 1.3 Other Functions

## **1.3.1 Hot Key Function**

| <b>Keys Combination</b> | Feature                    | Meaning                                                                                       |

|-------------------------|----------------------------|-----------------------------------------------------------------------------------------------|

| Fn + F1                 | Power down                 | Mini PCI power down                                                                           |

| Fn + F3                 | Reserve                    |                                                                                               |

| Fn + F4                 | Volume down                |                                                                                               |

| Fn + F5                 | Volume up                  |                                                                                               |

| Fn + F6                 | LCD/external CRT switching | Rotate display mode in LCD only, CRT only, and simultaneously display                         |

| Fn + F7                 | Brightness down            | Decreases the LCD brightness                                                                  |

| Fn + F8                 | Brightness up              | Increases the LCD brightness                                                                  |

| Fn + F10                | Mute                       | Audio Mute                                                                                    |

| Fn + F1 1               | Panel Off/On               | Toggle Panel on/off                                                                           |

| Fn + F12                | Suspend to DRAM / HDD      | Force the computer into either Suspend to HDD or Suspend to DRAM mode depending on BIOS Setup |

## 1.3.2 Power On/Off/Suspend/Resume Button

## **1.3.2.1 APM Mode**

At APM mode, power button is on/off system power.

### **1.3.2.2 ACPI Mode**

At ACPI mode, Windows power management control panel set power button behavior.

You could set "standby", "power off" or "hibernate" (must enable hibernate function in power management) to power button function.

Continue pushing power button over 4 seconds will force system off at ACPI mode.

## 1.3.3 Cover Switch

System automatically provides power saving by monitoring Cover Switch. It will save battery power and prolong the usage time when user closes the notebook cover.

At ACPI mode there are four functions to be chosen at windows power management control panel.

- 1. None

- 2. Standby

- 3. Off

- 4. Hibernate (must enable hibernate function in power management)

## 1.3.4 LED Indicators

#### 1.3.4.1 Five LED Indicators at Front Side:

From left to right that indicates POWER, Battery Status, HDD/CD-ROM, NUM LOCK, CAP LOCK, SCROLL LOCK, WLAN.

#### -- POWER:

This LED lights bule when the notebook was powered by AC or battery power line, Flashes orange (on 1 second, off 1 second) when entered suspend to RAM state. The LED is off when the notebook is in power off state.

#### -- BATTERY STATUS:

With battery operation, this LED stays off. When the battery charge drops to 10% of capacity, the LED lights red, flashes per 1 second and beeps per 2 second. When AC is connected, this indicator glows blue if the battery pack is fully charged or orange (amber) if the battery is being charged.

System has five status LED indicators at front side which to display system activity. HDD/CD-ROM, NUM LOCK, CAPS LOCK, SCROLL LOCK and WLAN.

## 1.3.5 Battery Status

## 1.3.5.1 Battery Warning

System also provides Battery capacity monitoring and gives users a warning signal to alarm they to store data before battery dead. This function also protects system from mal-function while battery capacity is low.

Battery Warning: Capacity below 10%, Battery Capacity LED flashes per second, system beeps per 2 seconds.

System will Suspend to HDD after 2 Minutes to protect users data.

## 1.3.5.2 Battery Low State

After Battery Warning State, and battery capacity is below 5%, system will generate beep sound for twice per second.

## 1.3.5.3 Battery Dead State

When the battery voltage level reaches 8.56 volts, system will shut down automatically in order to extend the battery packs' life.

## 1.3.6 Fan Power on/off Management

FAN is controlled by W83L951DG embedded controller-using ADM1032 to sense CPU temperature and PWM control fan speed. Fan speed is depended on CPU temperature. Higher CPU temperature faster Fan Speed.

## 1.3.7 CMOS Battery

CR2032 3V 220mAh lithium battery

When AC in or system main battery inside, CMOS battery will consume no power.

AC or main battery not exists, CMOS battery life at less (220mAh/5.8uA) 4 years.

## 1.3.8 I/O Port

- One Power Supply Jack

- One External CRT Connector For CRT Display

- Supports four USB port for all USB devices

- One MODEM RJ-11 phone jack for PSTN line

- One RJ-45 for LAN

- One IEEE1394 port

- One S/PDIF Jack.

- One Microphone Input Jack.

- One S-Video (PAL/NTSC) connector

- One Express Card Jack

- \* Two MINI PCI-E Jack for WLAN & TV Tuner Card

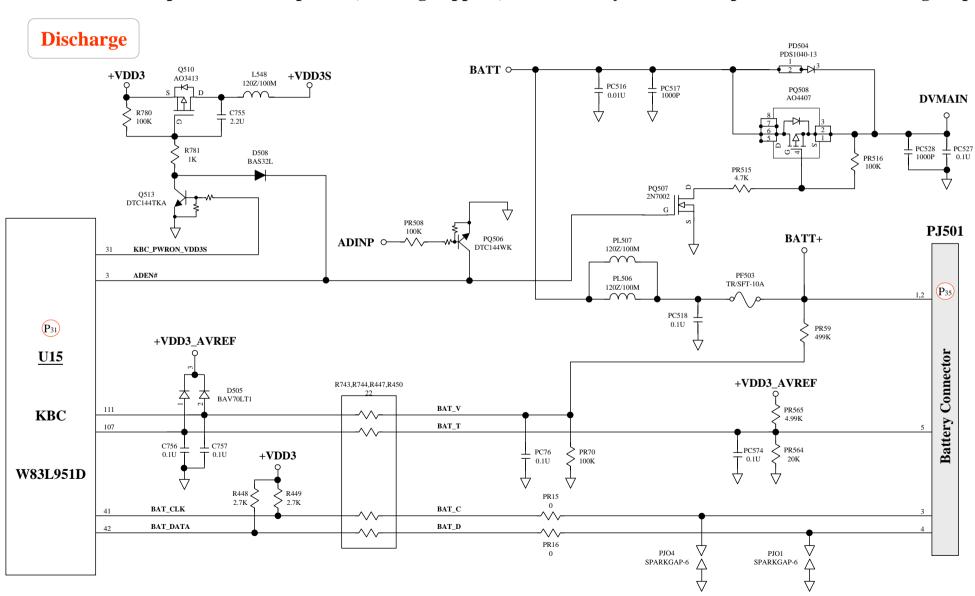

## 1.3.9 Battery Current Limit and Learning

Implanted H/W current limit and battery learning circuit to enhance protection of battery.

## 1.4 Power Management

The 8224 system has built in several power saving modes to prolong the battery usage for mobile purpose. User can enable and configure different degrees of power management modes via ROM CMOS setup (booting by pressing F2 key). Following are the descriptions of the power management modes supported.

## 1.4.1 System Management Mode

#### Photo detector and preamplifier in onepackage

• In this mode, each device is running with the maximal speed. CPU clock is up to its maximum.

#### Doze Mode

- In this mode, CPU will be toggling between on & stop grant mode either. The technology is clock throttling.

- This can save battery power without loosing much computing capability.

- The CPU power consumption and temperature is lower in this mode.

#### Standby Mode

• For more power saving, it turns of the peripheral components. In this mode, the following is the status of each device:

-- CPU: Stop grant

-- LCD: backlight off

-- HDD: spin down

### Suspend to DRAM

- The most chipset of the system is entering power down mode for more power saving. In this mode, the following is the status of each device:

- 1. Suspend to DRAM

-- CPU: off

-- Intel 915GM: Partial off

-- VGA: Suspend

-- PCMCIA: Suspend

-- Audio: off

-- SDRAM: self refresh

#### 2. Suspend to HDD

- -- All devices are stopped clock and power-down

- -- System status is saved in HDD

- -- All system status will be restored when powered on again

## **1.4.2 Other Power Management Functions**

### HDD & Video access

System has the ability to monitor video and hard disk activity. User can enable monitoring function for video and/or hard disk individually. When there is no video and/or hard disk activity, system will enter next PMU state depending on the application. When the VGA activity monitoring is enabled, the performance of the system will have some impact.

# 1.5 Appendix 1: Intel ICH7-M GPIO Definitions (1)

| Pin Name | <b>Current Define</b> | Input/Output | Function                    | Power Well |

|----------|-----------------------|--------------|-----------------------------|------------|

| GPIO0    | PM_BMBUSY#            | I/O          | BM BUSY                     | CORE       |

| GPIO1    | MINIPCI_ACT#          | I/O          | MINIPCI in detect           | CORE       |

| GPIO2    | PCI_INTE#             | I/O          | PCI interrupt for LAN       | CORE       |

| GPIO3    | PCI_INTF#             | I/O          | PCI interrupt for MINIPCI   | CORE       |

| GPIO4    | PCI_INTG#             | I/O          | PCI interrupt for IEEE 1394 | CORE       |

| GPIO5    | PCI_INTH#             | I/O          | pull high for PCI           | CORE       |

| GPIO6    | W_DISABLE#            | I/O          | Wireless LAN disable        | CORE       |

| GPIO7    | SCI#                  | I/O          | Sytem Control Interrupt     | CORE       |

| GPIO8    | EXTSMI#               | I/O          | SMI signal for chipset      | RESUME     |

| GPIO9    | X                     | I/O          | X                           | RESUME     |

| GPIO10   | X                     | I/O          | X                           | RESUME     |

| GPIO11   | SMBALERT#             | I/O          | SMBus alert                 | RESUME     |

| GPIO12   | X                     | I/O          | X                           | RESUME     |

| GPIO13   | X                     | I/O          | X                           | RESUME     |

| GPIO14   | X                     | I/O          | X                           | RESUME     |

| GPIO15   | TV_DISABLE#           | I/O          | TV disable                  | RESUME     |

| GPIO16   | DPRSLPVR              | I/O          | Deeper Sleep                | CORE       |

| GPIO17   | X                     | I/O          | X                           | CORE       |

| GPIO18   | STOP_PCI#             | I/O          | PCI stop                    | CORE       |

| GPIO19   | PANEL_ID1             | I/O          | Panel ID                    | CORE       |

| GPIO20   | STOP_CPU#             | I/O          | CPU stop                    | CORE       |

| GPIO21   | PANEL_ID0             | I/O          | Panel ID                    | CORE       |

| GPIO22   | PCI_REQ4#             | I/O          | PCI Request                 | CORE       |

| GPIO23   | CRT_IN#               | I/O          | CRT detect                  | CORE       |

| GPIO24   | X                     | I/O          | X                           | RESUME     |

| GPIO25   | SPK_OFF               | I/O          | Speak off                   | RESUME     |

| GPIO26   | SB_BT_ON#             | I/O          | Blue Tooth in detect        | RESUME     |

# 1.5 Appendix 1: Intel ICH7-M GPIO Definitions (2)

| Pin Name | <b>Current Define</b> | Input/Output | Function            | Power Well |

|----------|-----------------------|--------------|---------------------|------------|

| GPIO27   | X                     | I/O          | X                   | RESUME     |

| GPIO28   | X                     | I/O          | X                   | RESUME     |

| GPIO29   | X                     | I/O          | X                   | RESUME     |

| GPIO30   | X                     | I/O          | X                   | RESUME     |

| GPIO31   | X                     | I/O          | X                   | RESUME     |

| GPIO32   | PCLKRUN#              | I/O          | Clock run           | CORE       |

| GPIO33   | WIRELESS_PD#          | I/O          | Wireless power down | CORE       |

| GPIO34   | LAN_ENABLE#           | I/O          | LAN enable          | CORE       |

| GPIO35   | X                     | I/O          | X                   | CORE       |

| GPIO36   | PANEL_ID2             | I/O          | Panel ID            | CORE       |

| GPIO37   | X                     | I/O          | X                   | CORE       |

| GPIO38   | MB_ID0                | I/O          | Mother Board ID     | CORE       |

| GPIO39   | MB_ID1                | I/O          | Mother Board ID     | CORE       |

| GPIO48   | X                     | I/O          | X                   | CORE       |

| GPIO49   | HPWRGD                | I/O          | CPU power good      | V_CPU_IO   |

# 1.6 Appendix 2: W83L951DG GPIO Pins Definitions (1)

| Pin Name  | Pin No. | 915 Pin Definitions | I/O | Hi/Low | Function                  |

|-----------|---------|---------------------|-----|--------|---------------------------|

| Port 0    |         |                     |     |        |                           |

| GP00      | 94      | KB OUT 0            | О   |        | Key matrix scan output 0  |

| GP01      | 93      | KB OUT 1            | О   |        | Key matrix scan output 1  |

| GP02      | 92      | KB OUT 2            | O   |        | Key matrix scan output 2  |

| GP03      | 91      | KB OUT 3            | О   |        | Key matrix scan output 3  |

| GP04      | 90      | KB OUT 4            | О   |        | Key matrix scan output 4  |

| GP05      | 89      | KB OUT 5            | О   |        | Key matrix scan output 5  |

| GP06      | 88      | KB OUT 6            | О   |        | Key matrix scan output 6  |

| GP07      | 87      | KB OUT 7            | О   |        | Key matrix scan output 7  |

| Port 1    |         |                     |     |        |                           |

| GP10      | 86      | KB OUT 8            | O   |        | Key matrix scan output 8  |

| GP11      | 85      | KB OUT 9            | О   |        | Key matrix scan output 9  |

| GP12      | 84      | KB OUT 10           | О   |        | Key matrix scan output 10 |

| GP13      | 83      | KB OUT 11           | 0   |        | Key matrix scan output 11 |

| GP14      | 82      | KB OUT 12           | 0   |        | Key matrix scan output 12 |

| GP15      | 81      | KB OUT 13           | 0   |        | Key matrix scan output 13 |

| GP16      | 80      | KB OUT 14           | O   |        | Key matrix scan output 14 |

| GP17      | 79      | KB OUT 15           | О   |        | Key matrix scan output 15 |

| Port 2    |         |                     |     |        |                           |

| GP20      | 77      | MALL_KEY            | I   |        | MALL quick key            |

| GP21      | 76      | IE_KEY              | I   |        | IE quick key              |

| GP22      | 75      |                     | I   |        |                           |

| GP23      | 74      |                     | I   |        |                           |

| GP24/PWM0 | 73      | KBC_BEEP            |     |        | KBC beep                  |

| GP25/PWM1 | 72      |                     |     |        |                           |

| GP26/PWM2 | 71      | FAN#                | О   |        | Fan power PWM control     |

# 1.6 Appendix 2: W83L951DG GPIO Pins Definitions (2)

| Pin Name       | Pin No. | 915 Pin Definitions | I/O | Hi/Low    | Function                                   |

|----------------|---------|---------------------|-----|-----------|--------------------------------------------|

| GP27/PWM3      | 70      |                     | О   |           |                                            |

| Port 3         |         |                     |     |           |                                            |

| GP30           | 102     | KEY IN 0            | I   | Pull High | Key matrix input 0                         |

| GP31           | 101     | KEY IN 1            | I   | Pull High | Key matrix input 1                         |

| GP32           | 100     | KEY IN 2            | I   | Pull High | Key matrix input 2                         |

| GP33           | 99      | KEY IN 3            | I   | Pull High | Key matrix input 3                         |

| GP34           | 98      | KEY IN 4            | I   | Pull High | Key matrix input 4                         |

| GP35           | 97      | KEY IN 5            | I   | Pull High | Key matrix input 5                         |

| GP36           | 96      | KEY IN 6            | I   | Pull High | Key matrix input 6                         |

| GP37           | 95      | KEY IN 7            | I   | Pull High | Key matrix input 7                         |

| Port 4         |         |                     |     |           |                                            |

| GP40/FAN_TACH0 | 68      | FAN_SPEED           | I   |           | Fan speed input                            |

| GP41/FAN_TACH1 | 67      |                     |     |           |                                            |

| GP42/RXD       | 66      | KBC_RX              | I   |           | For firmware debug (请留焊点)                  |

| GP43/TXD       | 65      | KBC_TX              | O   |           | For firmware debug (请留焊点)                  |

| GP44/KBRST#    | 64      | HRCIN#              | О   |           | CPU Reset                                  |

| GP45/GATE_A20  | 63      | A20GATE             | О   |           | System A 20 Gate                           |

| GP46/CLKRUN#   | 62      | PCLKRUN#            |     |           | LPC Clock Run                              |

| GP47/LPCPD#    | 61      | LPCPD               |     |           | LPC Power-Down                             |

| Port 5         |         |                     |     |           |                                            |

| GP50           | 121     | EXTSMI#             | О   |           | External SMI#                              |

| GP51           | 120     | H8_SCI              |     |           | Need invert to SCI# sending to SouthBridge |

| GP52           | 119     | H8_WAKE_IP#         | О   |           | Wake-up SouthBridge at ACPI mode           |

| GP53           | 118     | H8_THRM#            | О   |           | Thermal throttling control to SouthBridge  |

| GP54           | 117     |                     | О   |           |                                            |

# 1.6 Appendix 2: W83L951DG GPIO Pins Definitions (3)

| Pin Name      | Pin No. | 915 Pin Definitions | I/O | Hi/Low        | Function                             |

|---------------|---------|---------------------|-----|---------------|--------------------------------------|

| GP55          | 116     |                     |     |               |                                      |

| GP56/DA0      | 114     | BLADJ               | О   |               | Backlight inverter brightness adjust |

| GP57/DA1      | 113     | I_CTRL              | O   |               | Charging current adjust              |

| Port 6        |         |                     |     |               |                                      |

| GP60/AD0      | 111     | BAT_VOLT            | I   |               | Battery voltage meansure             |

| GP61/AD1      | 110     | I_LIMIT             | I   |               | I-Limit function                     |

| GP62/AD2      | 109     | PWRGD               | I   |               | Monitor system on/off state          |

| GP63/AD3      | 108     | Vtt                 | I   |               | System Vtt voltage                   |

| GP64/AD4      | 107     | BAT_TEMP            | I   |               | Battery thermister temperature       |

| GP65/AD5      | 106     |                     | I   |               |                                      |

| GP66/AD6      | 105     |                     | I   |               |                                      |

| GP67/AD7      | 104     |                     | I   |               |                                      |

| Port 7        |         |                     |     |               |                                      |

| GP70/PS2_1CLK | 48      | T_CLK               | I/O | Pull High +5V | TouchPAD Clock                       |

| GP71/PS2_1DAT | 47      | T_DATA              | I/O | Pull High +5V | TouchPAD Data                        |

| GP72/PS2_2CLK | 46      |                     |     |               |                                      |

| GP73/PS2_2DAT | 45      | PWROK               | O   |               | Power OK                             |

| GP74/PS2_3CLK | 44      | SUSB_VGA_C          | Ο   |               | SUSB VGA Power                       |

| GP75/PS2_3DAT | 43      | SUSB0.9V            | O   |               | SUSC 0.9V                            |

| GP76/SDA0     | 42      | BAT_DATA            | I/O | Pull High +5V | SMBus Data                           |

| GP77/SCL0     | 41      | BAT_CLK             | I/O | Pull High +5V | SMBus Clock                          |

| Port 8        |         |                     |     |               |                                      |

| GP80/SDA1     | 40      | H8_THRM_DATA        |     |               | Reserve for SMBus Data               |

| GP81/SCL1     | 39      | H9_THRM_CLK         |     |               | Reserve for SMBus Clock              |

| GP82/CNTR0    | 38      |                     |     |               | Reserve for Fan0 Speed detect        |

# 1.6 Appendix 2: W83L951DG GPIO Pins Definitions (4)

| Pin Name       | Pin No. | 915 Pin Definitions | I/O | Hi/Low | Function                      |

|----------------|---------|---------------------|-----|--------|-------------------------------|

| GP83/CNTR1     | 37      |                     |     |        | Reserve for Fan1 Speed detect |

| GP84/CIR_RX    | 36      | CIR_RX              | I   |        | CIR Receiver                  |

| GP85           | 35      | LEARNING            | O   |        | Auto-Learning                 |

| GP86           | 34      | CHARGING            | О   |        | Battery charge control        |

| GP87           | 33      | H8_ENABKL           | O   |        | Enable Backlight              |

| Port 9         |         |                     |     |        |                               |

| GP90           | 31      | KBC_PWRON_VDD3S     | О   |        | Turn on VDD3.3 and VDD1.5     |

| GP91           | 30      | H8_RSMRST           | O   |        | SouthBridge RSMRST#           |

| GP92           | 29      | ICH_PWRBTN#         | O   |        | SouthBridge power button      |

| GP93           | 28      | SUSB1.5V            | О   |        | SUSB 1.5V                     |

| GP94           | 27      | SUSB1.8V            | О   |        | SUSC 1.8V                     |

| GP95           | 26      | SW_VDD3             | O   |        | VDD3 power source switch      |

| GP96           | 25      | SUSB_VCC_CORE       | O   |        | SUSB VCC CORE                 |

| GP97           | 24      | SUDB1.8V            | O   |        | SUSB 1.8V                     |

| Port A         |         |                     |     |        |                               |

| GPA0/EXTINT10  | 22      | DCON5V              | О   |        | DC ON 5V                      |

| GPA 1/EXTINT11 | 21      | DCON3V              | O   |        | DC ON 3V                      |

| GPA2/EXTINT12  | 20      | SUSB2.5V            | O   |        | SUSB 2.5V                     |

| GPA3/EXTINT13  | 19      | SUSB_VCCP           | О   |        | SUSB 1.05V                    |

| GPA4/EXTINT14  | 18      | SUSB3V              | О   |        | SUSB 3V                       |

| GPA5/EXTINT15  | 17      | SUSB5V              | О   |        | SUSB 5V                       |

| GPA6/EXTINT16  | 16      | SUSC1.2V            | О   |        | SUSC 1.2V                     |

| GPA7/EXTINT17  | 15      | SUSB1.2V            | О   |        | SUSB 1.2V                     |

| Port B         |         |                     |     |        |                               |

| GPB0/EXTINT20  | 14      | CAP#                | О   |        | Capitals Lock LED indicator   |

# 1.6 Appendix 2: W83L951DG GPIO Pins Definitions (5)

| Pin Name      | Pin No. | 915 Pin Definitions | I/O | Hi/Low    | Function                                                                                                                  |

|---------------|---------|---------------------|-----|-----------|---------------------------------------------------------------------------------------------------------------------------|

| GPB1/EXTINT21 | 13      | NUM#                | О   |           | Numeral Lock LED indicator                                                                                                |

| GPB2/EXTINT22 | 12      | SCROLL#             | О   |           | Scroll Lock LED indicator                                                                                                 |

| GPB3/EXTINT23 | 11      | BATT_R#             | О   |           | Battery Charger Red LED indicator                                                                                         |

| GPB4/EXTINT24 | 10      | BATT_G#             | О   |           | Battery Charger Green LED indicator                                                                                       |

| GPB5/EXTINT25 | 9       |                     |     |           |                                                                                                                           |

| GPB6/EXTINT26 | 8       | AC_BATT_POWER#      | О   |           | Power LED indicator                                                                                                       |

| GPB7/EXTINT27 | 7       |                     |     |           |                                                                                                                           |

| Port C        |         |                     |     |           |                                                                                                                           |

| GPC0/EXTINT30 | 6       | PWRBTN#             | I   | Pull High | Power Button                                                                                                              |

| GPC1/EXTINT31 | 5       | H8_SUSB#            | I   |           | Invert from SUSA# to wake up KBC when system resumed by MDC modem and internal LAN. Inform system powe management status. |

| GPC2/EXTINT32 | 4       | SUSC#               | I   |           | System to S4 (soft off) or S5                                                                                             |

| GPC3/EXTINT33 | 3       | ADEN#               | I   |           | AC adapter in detect                                                                                                      |

| GPC4/EXTINT34 | 2       | BATT_DEAD#          | I   |           | Battery low detect                                                                                                        |

| GPC5/EXTINT35 | 1       | H8_LIDSW#           | I   |           | Cover s witch                                                                                                             |

| GPC6/EXTINT36 | 128     | INSTAND_KEY         | I   |           | INSTAND quick key                                                                                                         |

| GPC7/EXTINT37 | 127     | CIR_RX              | I   |           | CIR RX                                                                                                                    |

# 2. System View and Disassembly

## 2.1 System View

### 2.1.1 Front View

- **1** Microphone Jack

- **2** Line In Jack

- **3** SPDIF Jack

- **4** Blue Tooth

- CRT Connector

- 2 IEEE1394 Port

- **3** Ventilation Openings

- **4** BTWIRE Switch

- **5** TV-out Connector

- **6** RJ45/RJ11 Connector

- **7** USB Port

- **8** CardReader Socket

- New Card Socket

## 2.1.3 Right-side View

- DVD-ROM Drive

- USB Port

- Power Connector

## 2.1.4 Rear View

- TV antenna Connector

- USB Ports \*2

- Kensington Lock

- DVI Connector

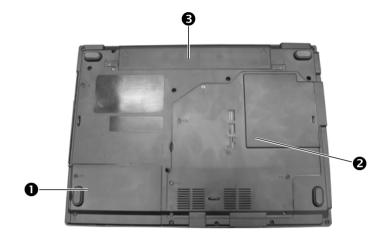

## 2.1.5 Bottom View

- Hard Disk Drive

- 2 DDR/CPU/Wireless LAN Card/TV Card

- **3** Battery Park

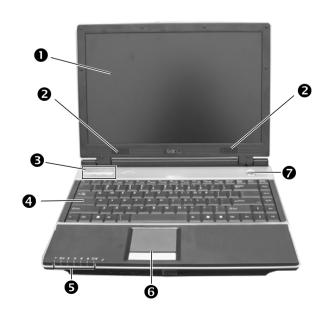

## 2.1.6 Top-open View

- LCD Screen

- 2 Speaker Set

- 3 Instand/Mail/P1 Key

- **4** Keyboard

- **6** Device LED Indicators

- 6 Touch Pad

- **7** Power Button

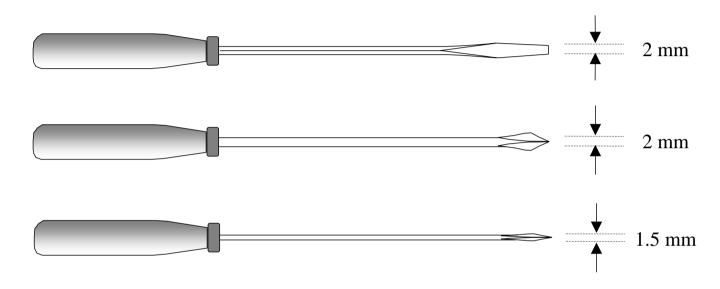

## 2.2 Tools Introduction

1. Minus screw driver with bit size 2 mm and 1.5 mm for notebook assembly & disassembly. . .

2. Auto screw driver for notebook assembly & disassembly.

| Screw Size | Tooling           | Tor.                       | Bit Size |

|------------|-------------------|----------------------------|----------|

| 1. M2.0    | Auto-Screw driver | 2.0-2.5 kg/cm <sup>2</sup> | #0       |

## 2.3 System Disassembly

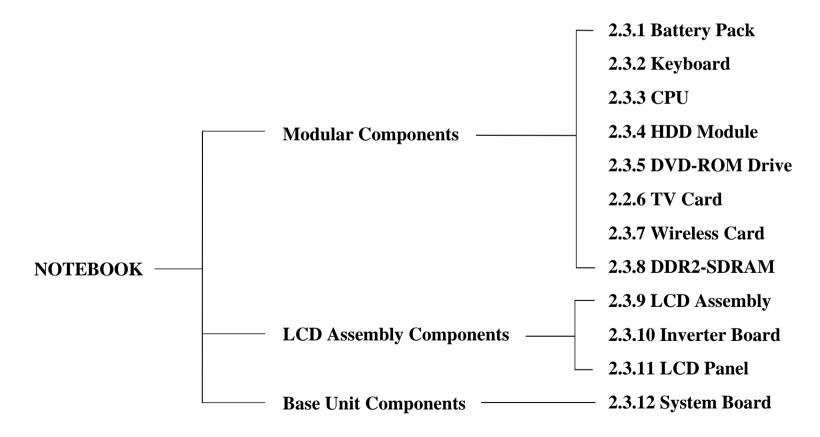

The section discusses at length each major component for disassembly/reassembly and show corresponding illustrations. Use the chart below to determine the disassembly sequence for removing components from the notebook.

**NOTE:** Before you start to install/replace these modules, disconnect all peripheral devices and make sure the notebook is not turned on or connected to AC power.

## 2.3.1 Battery Pack

### **Disassembly**

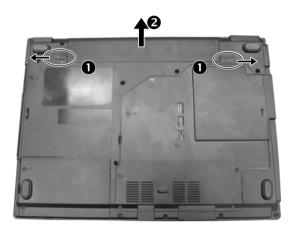

- 1. Carefully put the notebook upside down.

- 2. Slide the two release lever outwards to the "unlock" (1) position (1), while take the battery pack out of the compartment (2). (Figure 2-1)

Figure 2-1 Remove the battery pack

- 1. Replace the battery pack into the compartment. The battery pack should be correctly connected when you hear a clicking sound.

- 2. Slide the release lever to the "lock" (☐) position.

## 2.3.2 Keyboard

## Disassembly

- 1. Remove the battery pack. (Refer to section 2.3.1 Disassembly)

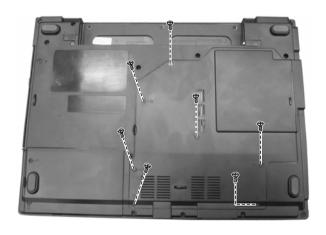

- 2. Remove the eight screws fastening the keyboard cover. (Figure 2-2)

- 3. Lift the keyboard cover up. (Figure 2-3)

Figure 2-2 Remove the eight screws

Figure 2-3 Lift the keyboard cover

4. Slightly lift up the keyboard, then disconnect the cable from the system board, then separate the keyboard. (Figure 2-4)

Figure 2-4 Lift the keyboard

- 1. Reconnect the keyboard cable and fit the keyboard back into place.

- 2. Replace the keyboard cover and secure with nine screws.

- 3. Replace the battery pack. (Refer to section 2.3.1 Reassembly)

## 2.3.3 CPU

## Disassembly

- 1. Remove the battery pack. (Refer to section 2.3.1 Disassembly)

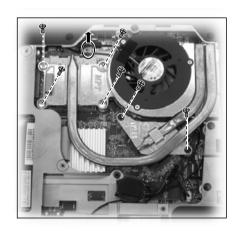

- 2. Remove the seven screws fastening the CPU cover. (Figure 2-5)

- 3. Remove the six spring screws that secure the heatsink upon the CPU and disconnect the fan's power cord from system board. (Figure 2-6)

Figure 2-5 Remove the seven screws

Figure 2-6 Free the heatsink

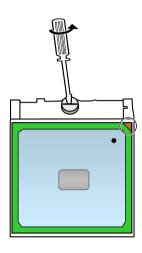

4. To remove the existing CPU, loosen the screw by a flat screwdriver, upraise the CPU socket to unlock the CPU. (Figure 2-7)

Figure 2-7 Remove the CPU

- 1. Carefully, align the arrowhead corner of the CPU with the beveled corner of the socket, then insert CPU pins into the holes. Tighten the screw by a flat screwdriver to locking the CPU.

- 2. Connect the fan's power cord to the system board, fit the heatsink upon the CPU and secure with six spring screws.

- 3. Replace the CPU cover and secure with seven screws.

- 4. Replace the battery pack. (Refer to section 2.3.1 Reassembly)

## 2.3.4 HDD Module

### **Disassembly**

- 1. Carefully put the notebook upside down. Remove the battery pack. (Refer to section 2.3.1 Disassembly)

- 2. Remove the two screws fastening the HDD compartment cover. (Figure 2-8)

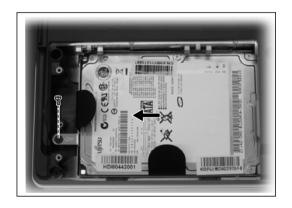

- 3. Remove one screw and slide the HDD module out of the compartment. (Figure 2-9)

Figure 2-8 Remove the HDD compartment cover

Figure 2-9 Remove HDD module

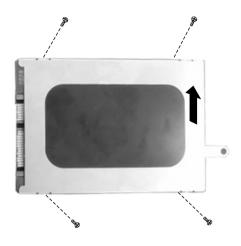

4. Remove the four screws to separate the hard disk drive from the bracket, remove the hard disk drive. (Figure 2-10)

Figure 2-10 Remove hard disk drive

- 1. Attach the bracket to hard disk drive and secure with four screws.

- 2. Slide the HDD module into the compartment and secure with one screw.

- 3. Replace the HDD compartment cover and secure with two screws.

- 4. Replace the battery pack. (Refer to section 2.3.1 Reassembly)

## 2.3.5 DVD-ROM Drive

#### Disassembly

- 1. Carefully put the notebook upside down. Remove the battery pack. (Refer to section 2.3.1 Disassembly)

- 2. Remove the one screw fastening the DVD-ROM drive. (Figure 2-11)

- 3. Insert a small rod, such as a straightened paper clip, into DVD-ROM drive's manual eject hole (●) and push firmly to release the tray. Then gently pull out the DVD-ROM drive by holding the tray that pops out (●). (Figure 2-11)

Figure 2-11 Remove the CD/DVD-ROM drive

- 1. Push the DVD-ROM drive into the compartment and secure with one screw.

- 2. Replace the battery pack. (Refer to section 2.3.1 Reassembly)

## **2.3.6 TV Card**

#### Disassembly

- 1. Carefully put the notebook upside down. Remove the battery pack. (Refer to section 2.3.1 Disassembly)

- 2. Remove seven screws fastening the CPU cover. (Refer to step 2 of section 2.3.3 Disassembly)

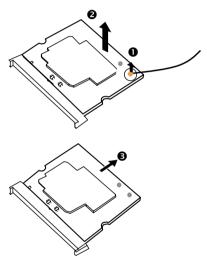

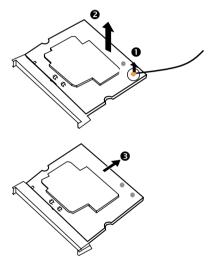

- 3. Disconnect the TV card's antennae first (**①**). Then pull up the TV card (**②**) and remove the TV card (**③**). (Figure 2-12)

Figure 2-12 Remove the TV card

- 1. To install the TV card, match the TV card 's notched part with the socket's projected part and firmly insert it into the socket. Then push down the TV card into position. Then make sure the antennae fully populated.

- 2. Replace seven screws to fasten the CPU cover. (Refer to step 3 of section 2.3.3 Reassembly)

- 3. Replace the battery pack. (Refer to section 2.3.1 Reassembly)

### 2.3.7 Wireless Card

#### Disassembly

- 1. Carefully put the notebook upside down. Remove the battery pack. (Refer to section 2.3.1 Disassembly)

- 2. Remove seven screws fastening the CPU cover. (Refer to step 2 of section 2.3.3 Disassembly)

- 3. Disconnect the wireless card's antennae first (**①**). Then pull up the wireless card (**②**) and remove the wireless card (**③**). (Figure 2-13)

Figure 2-13 Remove the wireless card

- 1. To install the wireless card, match the wireless card 's notched part with the socket's projected part and firmly insert it into the socket. Then push down the wireless card into position. Then make sure the antennae fully populated.

- 2. Replace seven screws to fasten the CPU cover. (Refer to step 3 of section 2.3.3 Reassembly)

- 3. Replace the battery pack. (Refer to section 2.3.1 Reassembly)

### **2.3.8 DDR2-SDRAM**

#### **Disassembly**

- 1. Carefully put the notebook upside down. Remove the battery pack. (See section 2.3.1 Disassembly)

- 2. Remove seven screws fastening the CPU cover. (Refer to step 2 of section 2.3.3 Disassembly)

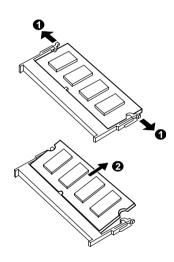

- 3. Pull the retaining clips outwards (1) and remove two SO-DIMM (2). (Figure 2-14)

Figure 2-14 Remove the SO-DIMM

- 1. To install the DDR2, match the DDR2's notched part with the socket's projected part and firmly insert the SO-DIMM into the socket at 20-degree angle. Then push down until the retaining clips lock the DDR2 into position.

- 2. Replace seven screws to fasten the CPU cover. (Refer to step 3 of section 2.3.3 Reassembly)

- 3. Replace the battery pack. (See section 2.3.1 Reassembly)

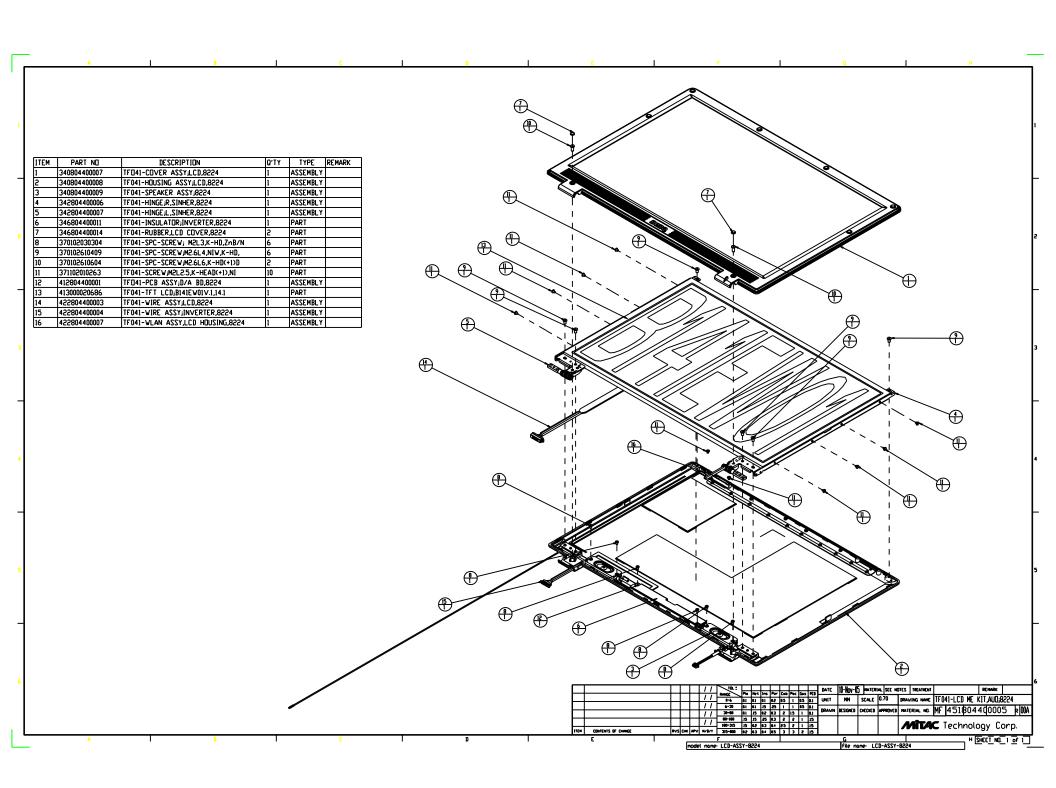

## 2.3.9 LCD Assembly

#### **Disassembly**

- 1. Remove the battery pack, keyboard, wireless card. (See sections 2.3.1, 2.3.2, and 2.3.7 Disassembly)

- 2. Remove five screws that secure the hinge and disconnect three cables. (Figure 2-15)

- 3. Carefully pull the antenna out. Now you can lift up the LCD assembly from base unit.

Figure 2-15 Free the LCD ASSY

- 1. Attach the LCD assembly to the base unit and secure with five screws.

- 2. Reconnect the three cables to the system board.

- 3. Replace the wireless card, keyboard and battery pack. (Refer to sections 2.3.7, 2.3.2 and 2.3.1 Reassembly)

## 2.3.10 Inverter Board

#### Disassembly

- 1. Remove the battery, keyboard, wireless card, LCD assembly. (Refer to section 2.3.1, 2.3.2, 2.3.7 and 2.3.9 Disassembly)

- 2. Remove the two rubber pads and two screws on the corners of the panel. (Figure 2-16)

- 3. Insert a flat screwdriver to the lower part of the LCD cover and gently pry the frame out. Repeat the process until the cover is completely separated from the housing.

- 4. Remove the two screws and disconnect the two cables to free the inverter board. (Figure 2-17)

Figure 2-16 Remove LCD cover

Figure 2-17 Remove the two screws and disconnect the two cables

#### Reassembly

- 1. Reconnect two cables. Fit the inverter board back into place and secure with two screws.

- 2. Fit the LCD cover and secure with two screws and rubber pads.

- 3. Replace the LCD assembly, wireless card, keyboard and battery pack. (Refer to sections 2.3.9, 2.3.7, 2.3.2 and 2.3.1 Reassembly)

#### **2.3.11 LCD Panel**

#### Disassembly

- 1. Remove the battery, keyboard, wireless card, LCD assembly and inverter board. (Refer to section 2.3.1, 2.3.2, 2.3.7, 2.3.9 and 2.3.10 Disassembly)

- 2. Remove six screws. (Figure 2-18)

- 3. Remove eight screws that secure the LCD bracket. (Figure 2-19)

Figure 2-18 Remove six screws

Figure 2-19 Remove eight screws

4. Disconnect the cable to free the LCD panel. (Figure 2-20)

Figure 2-20 Disconnect the cable

#### Reassembly

- 1. Replace the cable to the LCD.

- 2. Attach the LCD panel's bracket back to LCD panel and secure with eight screws.

- 3. Replace the LCD panel into LCD housing, fasten the LCD panel by six screws.

- 4. Replace the inverter board, LCD assembly, wireless card, keyboard, battery pack. (See sections 2.3.10, 2.3.9, 2.3.7, 2.3.2 and 2.3.1 Reassembly)

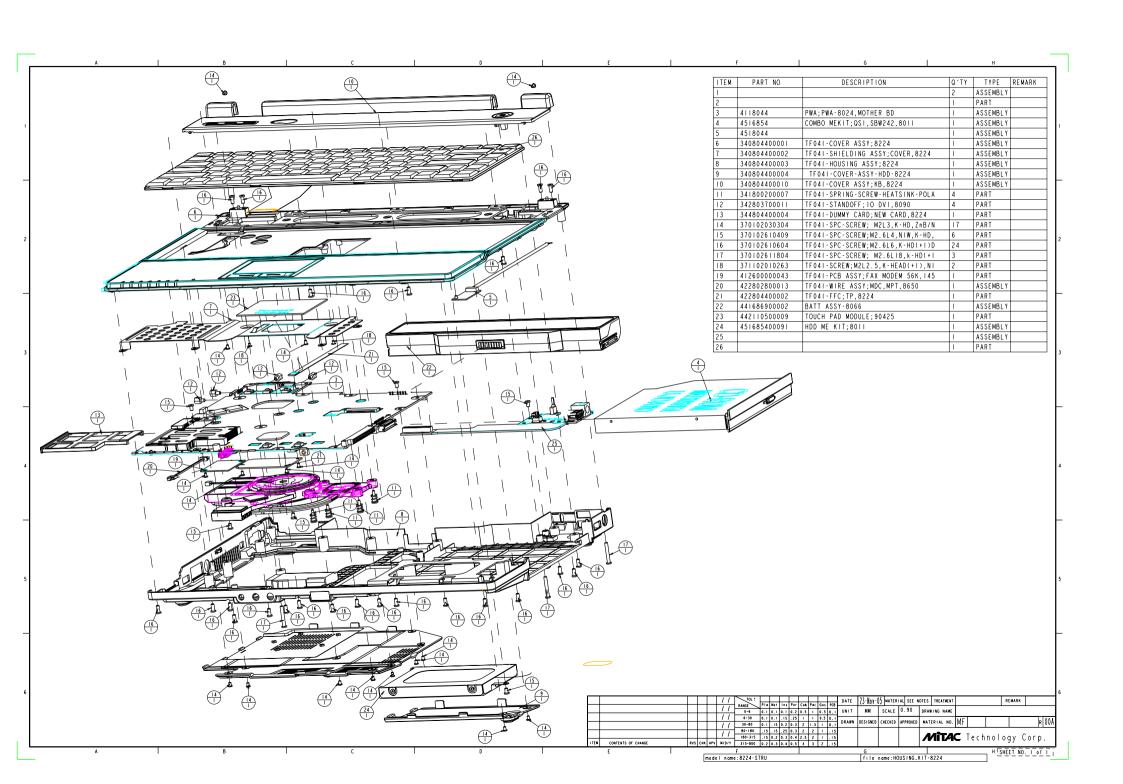

#### 2.3.12 System Board

#### **Disassembly**

- 1. Remove the battery pack, keyboard, CPU, HDD, DVD-ROM, TV card, wireless card, DDR2 and LCD assembly. (Refer to sections 2.3.1 ~ 2.3.9 Disassembly)

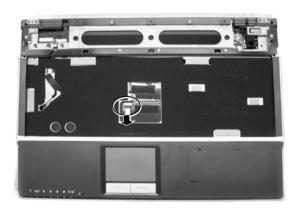

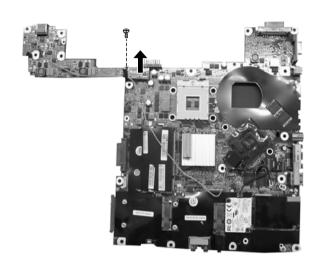

- 2. Disconnect the cable. (Figure 2-21)

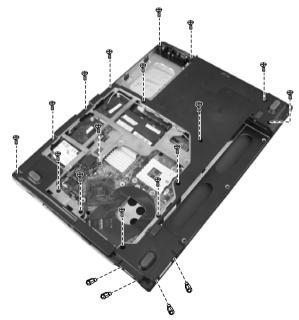

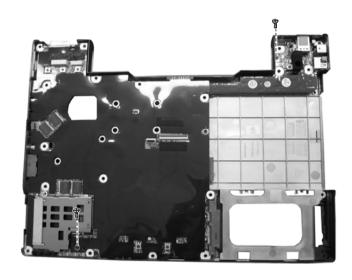

- 3. Carefully put the notebook upside down, remove the sixteen screws fastening the housing and four hex nuts fastening the housing. (Figure 2-22)

Figure 2-21 disconnect the cable

Figure 2-22 Remove the sixteen screws and four hex nuts

- 4. Remove the two screws and free the top cover. (Figure 2-23)

- 5. Carefully put the system board upside down and remove one screw. Then separate the bracket, now you can separate the daughter board from system board. (Figure 2-24)

Figure 2-23 Remove the two screws

Figure 2-24 Free the daughter board

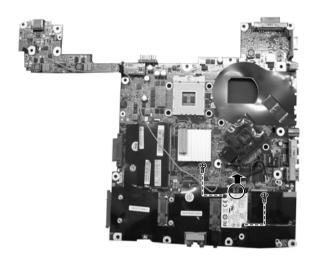

6. Remove two screws and disconnect the cable, now you can separate the modem board from system board and free the system board. (Figure 2-25)

Figure 2-25 Free the system board

#### Reassembly

- 1. Replace the modem board to the system board.

- 2. Replace the daughter board to the system board.

- 3. Replace the system board back into the housing and secure with two screws.

- 4. Replace the top cover into the housing and reconnect the touch pad's cable.

- 5. Secure with sixteen screws and four hex nuts fasten the housing.

- 6. Replace the LCD assembly, DDR2, Wireless Card, TV card, DVD-ROM, HDD, CPU, keyboard and battery pack. (Refer to previous section reassembly)

#### 3. Definition & Location of Connectors/Switches

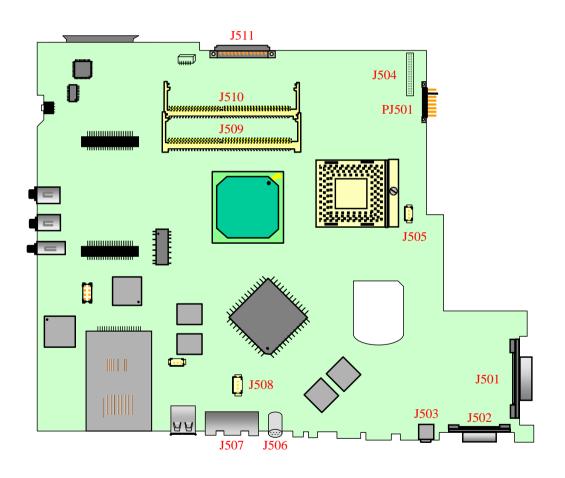

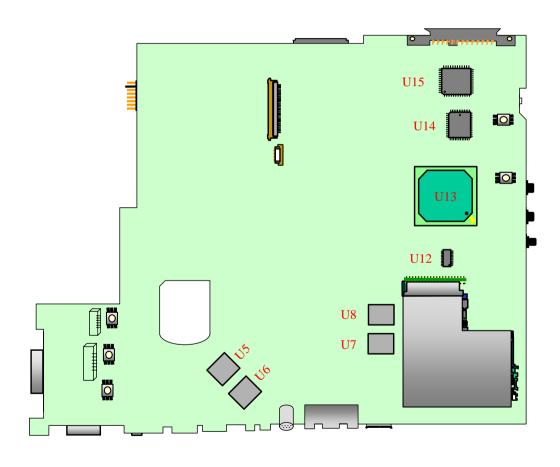

#### 3.1 Mother Board-A (1)

- **PJ501: Battery Connector**

- **J501: CRT Connector**

- **J502: DVI Connector**

- **♦ J503: IEEE 1394 Connector**

- **#** J504: Board to Board Connector

- **4** J505: CPU Fan Connector

- **4** J506: TV-Out Connector

- **♦ J507: RJ45/RJ11 Connector**

- J508: RJ45 Jump Wire Connector

- **♦ J509, J510: Extend DDR2 SDRAM Socket**

- **\$\Phi\$** J511: Secondary IDE Connector

---- To next page -----

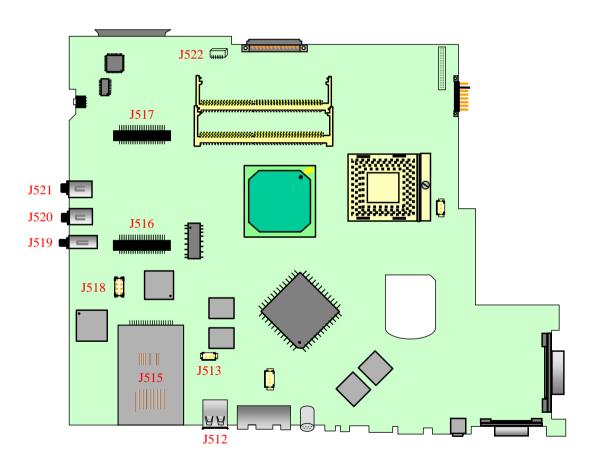

#### 3. Definition & Location of Connectors/Switches

#### 3.1 Mother Board-A (2)

#### ----- Continued to previous page -----

- **\$ J512: USB Port**

- **4** J513: RTC Connector

- **\$\Pi\$** J515: CardReader Slot

- **\$\Pi\$** J516: Wireless LAN Connector

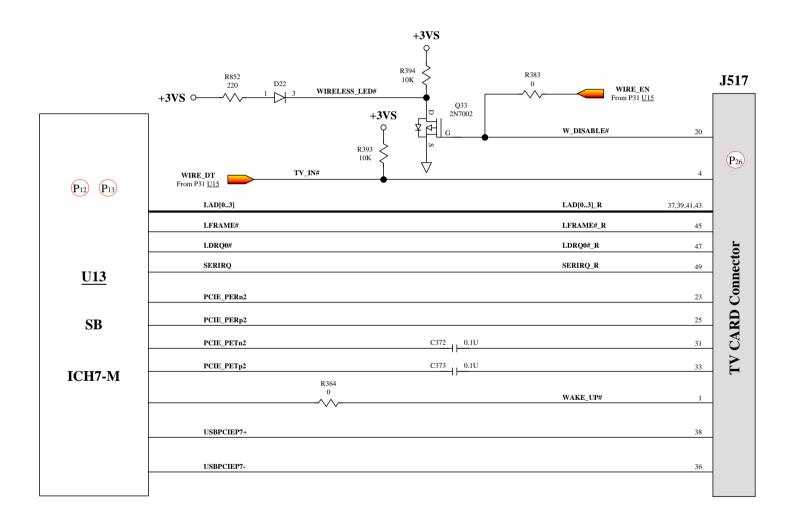

- **4** J517: TV Card Connector

- **4** J518: MDC Board Connector

- **\$\Pi\$** J519: SPDIF Jack

- **4** J520: Microphone Jack

- **4** J521: Line In Jack

- **\$\Phi\$** J522: Blue Tooth Connector

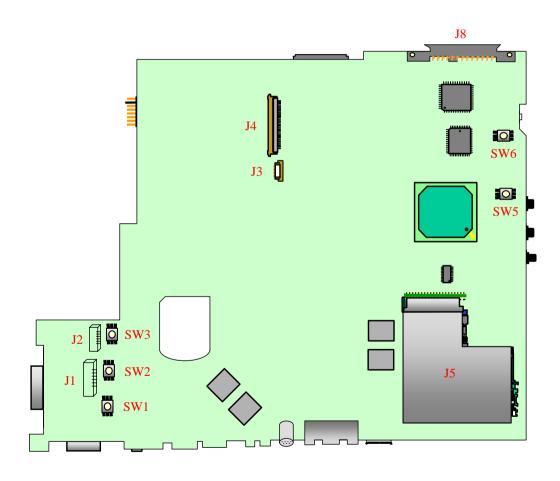

#### 3. Definition & Location of Connectors/Switches

#### 3.1 Mother Board-B

- **#** J1: LCD Inverter Connector

- **\$ J2: LCD Connector**

- **\$ J3: Touch Pad Connector**

- **4** J4: Internal Keyboard Connector

- **\$\Pi\$** J5: New Card Socket

- **4** J8: HDD Connector

- **SW1: Instand Key**

- SW2: Mail Key

- **\$ SW3: P1 Key**

- **SW5: Touch-Pad Left Button**

- **SW6: Touch-Pad Right Button**

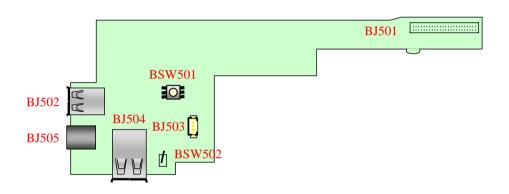

#### 3. Definition & Location of Connectors/Switches

#### 3.2 Daughter Board-A